Part Number: DP83822I

Tool/software:

Hi team,

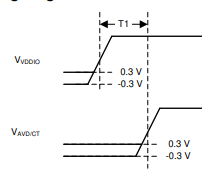

In my customer's ongoing design, 2.5V for VDDIO is generated from 3.3V powering AVD.

So it is impossible to wait for AVD ramp until VDDIO fully ramps up.

So my customer is wondering if it is allowed when VDDIO<AVD+0.3V is kept.

Could you please check it?

If this is not recommended, could you please advise how to address this?

Best regards,

Kazuki Itoh