Tool/software:

During remote downstream port access, we suspect the internal port state machine is stuck.

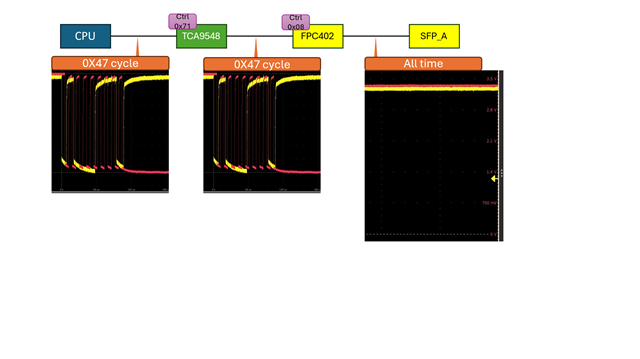

When the issue happens there is always NACK received after logical device I2C address is sent by Host, and also there is no any I2C signal in the downstream interface.

We captured the host side I2C waveform, found the SCL signal is not regularly driven, sometimes delayed for long time(keeping long “1” or “0”) during a whole byte transmission.

Also checked all the FPC402 registers, no abnormal information found.

Can you help to confirm if that SCL being interrupted will cause the port state machine stuck ?

Is there any register to indicating the stuck status ? We can not find this kind of register in the programmer guide.

Any workaround recommended to avoid this kind of stuck ?