Tool/software:

We designed an HDMI input/output board using a combination of the TMDS1204 and an AMD FPGA.

The HDMI compliance test was conducted by the HDMI certification body and the following FAILs were noted.

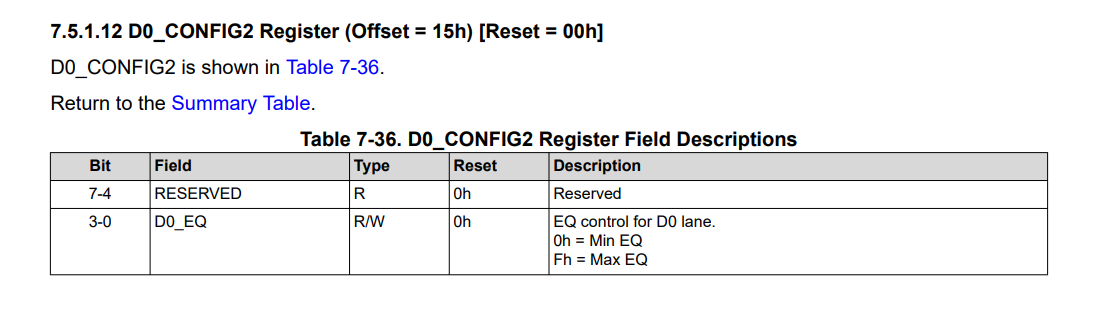

No.1 OUTPUT Test ID 7-4 TMDS - Trise, Tfall

The rise and fall times of Data0, Data1, and Data2 when outputting 3840x2160@30p signals are less than 70 ps compared to the spec of 75 ps or more.

From the TMDS1204 datasheet, I believe that this can be handled by changing the SLEW_3G_Register setting, am I correct?

If possible, please let me know the results of your evaluation of how much changing the SLEW_3G_Register setting changes the rise and rise time when outputting 3840x2160@30p.

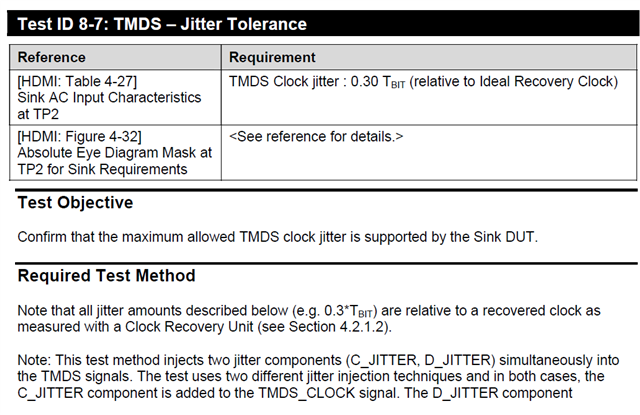

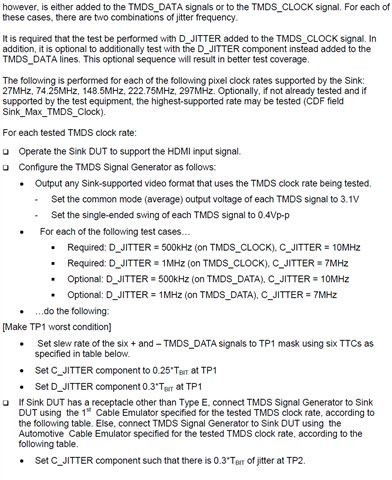

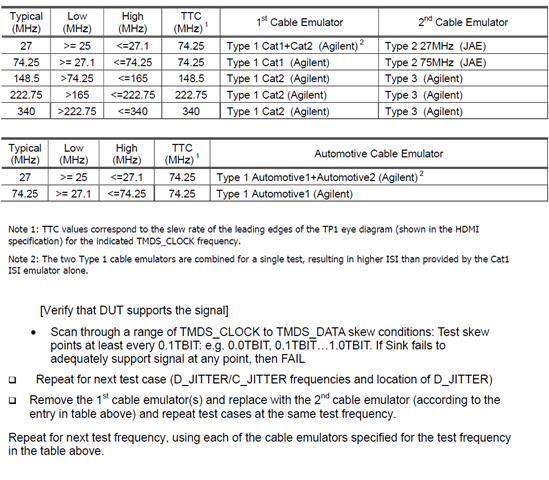

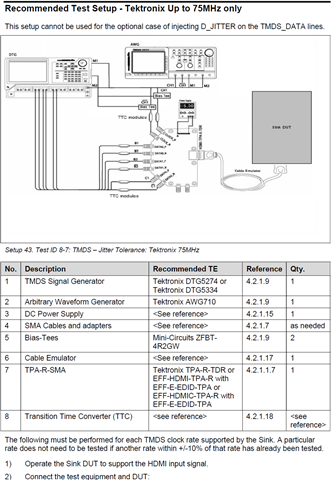

No.2 INPUT Test ID 8-7: TMDS – Jitter Tolerance

Only the 27M Type 2 27MHz (JAE) configuration FAILed, while the 27M Type 1 Cat1+Cat2 (Agilent) configuration and 74M, 148M, 222M, 297M PASSED.

Initially, I thought that the FPGA lacked jitter tolerance, so I contacted AMD, but they assured me that the FPGA would not be able to receive the data without jitter cleaning with Redriver.

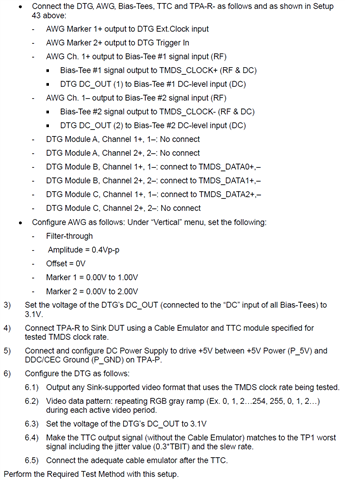

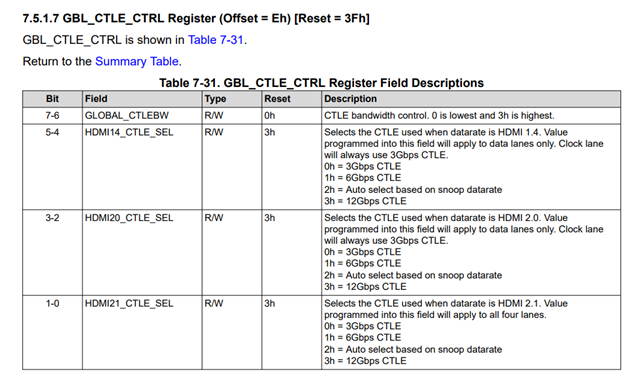

I referred to the datasheet but could not find a good setting to increase jitter tolerance at low transmission rates. Please let me know what to try.