Tool/software:

Test IOP part TC 8, the three items regarding link up time do not meet the specifications. All exceed the maximum linkup time.

May I ask if your company has a solution or guidance for corrective measures on this matter?

Testing standard basis: 5.1.2 Link-up time in docs<OA_Automotive_Ethernet_ECU_TestSpecification_Layer_1_100BASE-T1_v3.0.pdf>

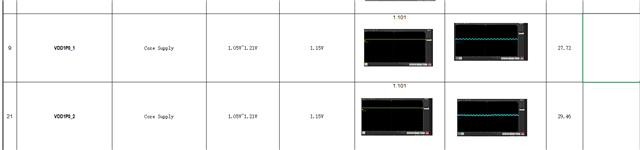

The current test results are as follows:

.........