Tool/software:

Hello TI,

We are using SN65DSI83 dsi-lvds bridge for LVDS display panel, where test pattern works well and for actual android display we are just able to see white bright screen as shown in the pictures.

We see register settings all looks good. but we are not seeing proper display. could you please help us to identify issue here.

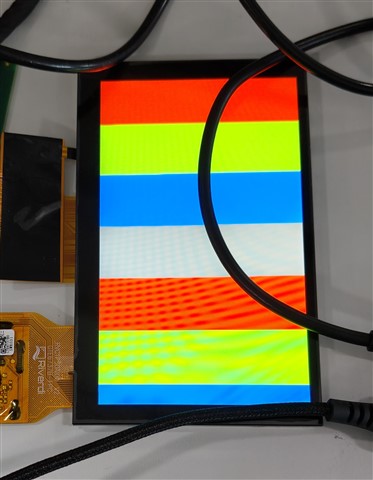

Test pattern,

Display during boot time, not for test pattern,

Logs:

console:/ # dmesg | grep sn65

[ 9.874410] <<<<<<<<<<<<<<<bridge drv : sn65dsi83_init>>>>>>>>>>>>>>>>>

[ 10.680681] sn65dsi83 0-002d: sn65dsi83_probe

[ 10.685411] sn65dsi83 0-002d: failed to parse enable gpio

[ 10.691009] sn65dsi83 0-002d: sn65dsi83_brg_power_off

[ 10.716103] sn65dsi83 0-002d: sn65dsi83_brg_power_on

[ 10.732092] sn65dsi83 0-002d: sn65dsi83_read client 0xfffffff00d748a80

[ 10.739039] sn65dsi83 0-002d: sn65dsi83_read: read reg 0x09 data 0x00

[ 10.745519] sn65dsi83 0-002d: sn65dsi83_brg_reset ret=0

[ 10.750810] sn65dsi83 0-002d: sn65dsi83_brg_reset force_ret=0

[ 10.756590] sn65dsi83 0-002d: sn65dsi83_probe, force_ret=0

[ 10.762138] sn65dsi83 0-002d: sn65dsi83_brg_power_off

[ 10.788094] sn65dsi83_probe: call setup

[ 10.804145] <<<<<<<<<<<<<<<<sn65dsi drv: probe exit>>>>>>>>>>>>>>>>>>>>

[ 12.618177] <<<<<<<<<<<<<<<<<<<bridge drv : bridge_to_sn65dsi83>>>>>>>>>>>>>>>>>>>>

[ 12.618183] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_bridge_attach

[ 12.632126] <<<<<<<<<<<<sn65dsi drv : sn65dsi83_attach_dsi exit>>>>>>>>>>>>>>

[ 12.632132] sn65dsi83 0-002d: sn65dsi83_attach_dsi

[ 12.644639] <<<<<<<<<<<<<<<<sn65dsi drv : sn65dsi83_attach_dsi exit>>>>>>>>>>>>>>>>>>

[ 12.687290] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 12.687296] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_detect

[ 12.701241] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 12.701248] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_mode_valid: mode: 800*480@24600 is valid

[ 35.453997] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 35.454005] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_detect

[ 35.468184] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 35.468193] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_mode_valid: mode: 800*480@24600 is valid

[ 38.104943] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.104953] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_detect

[ 38.136013] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.136023] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_mode_valid: mode: 800*480@24600 is valid

[ 38.158080] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.158089] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_detect

[ 38.168815] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.168827] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_mode_valid: mode: 800*480@24600 is valid

[ 38.187829] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.187838] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_detect

[ 38.216921] <<<<<<<<<<<<<<<<bridge drv: connector_to_sn65dsi83>>>>>>>>>>>>>>>>>>

[ 38.216931] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_connector_mode_valid: mode: 800*480@24600 is valid

[ 44.561540] <<<<<<<<<<<<<<<<<<<bridge drv : bridge_to_sn65dsi83>>>>>>>>>>>>>>>>>>>>

[ 44.561555] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_bridge_mode_set: mode: 800*480@24600

[ 44.585008] <<<<<<<<<<<<<<<<<<<bridge drv : bridge_to_sn65dsi83>>>>>>>>>>>>>>>>>>>>

[ 44.585022] msm_drm 5e00000.qcom,mdss_mdp: sn65dsi83_bridge_enable

[ 44.591345] sn65dsi83 0-002d: sn65dsi83_brg_setup

[ 44.596133] sn65dsi83 0-002d: sn65dsi83_brg_power_on

[ 44.608172] sn65dsi83 0-002d: DSI clock [ 75000000 ] Hz

[ 44.613481] sn65dsi83 0-002d: Resolution [ 800 x 480 ]

[ 44.619089] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x09 data 0x00

[ 44.626038] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x0d data 0x00

[ 44.632763] sn65dsi83 0-002d: lvds_clk=25000000 lvds_clk_range=0x0

[ 44.639334] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x0a data 0x01

[ 44.646304] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x12 data 0x0f

[ 44.653213] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x13 data 0x00

[ 44.659936] sn65dsi83 0-002d: dsi_clk_range=0xf

[ 44.664557] sn65dsi83 0-002d: dsi_clk_div=0x2

[ 44.669298] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x0b data 0x10

[ 44.675984] sn65dsi83 0-002d: sn65dsi83_read client 0xfffffff00d748a80

[ 44.682950] sn65dsi83 0-002d: sn65dsi83_read: read reg 0x10 data 0x3e

[ 44.689741] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x10 data 0x26

[ 44.696713] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x11 data 0x00

[ 44.711725] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x18 data 0x1f

[ 44.718842] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x19 data 0x00

[ 44.732877] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x1a data 0x03

[ 44.739816] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x1b data 0x00

[ 44.746789] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x28 data 0x21

[ 44.753772] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x29 data 0x00

[ 44.760747] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2a data 0x00

[ 44.767704] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2b data 0x00

[ 44.774665] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x20 data 0x20

[ 44.781658] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x21 data 0x03

[ 44.788621] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x22 data 0x00

[ 44.795592] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x23 data 0x00

[ 44.802594] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x24 data 0xe0

[ 44.809552] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x25 data 0x01

[ 44.816476] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x26 data 0x00

[ 44.823445] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x27 data 0x00

[ 44.830498] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2c data 0x6e

[ 44.837418] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2d data 0x00

[ 44.844363] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2e data 0x00

[ 44.851327] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x2f data 0x00

[ 44.858282] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x30 data 0x14

[ 44.865203] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x31 data 0x00

[ 44.872191] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x32 data 0x00

[ 44.879136] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x33 data 0x00

[ 44.886200] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x34 data 0x08

[ 44.893148] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x36 data 0x08

[ 44.900143] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x35 data 0x00

[ 44.907072] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x37 data 0x00

[ 44.914103] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x38 data 0x08

[ 44.921056] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x3a data 0x08

[ 44.928169] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x39 data 0x00

[ 44.935091] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x3b data 0x00

[ 44.942049] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x3d data 0x00

[ 44.949033] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x3e data 0x00

[ 44.955786] sn65dsi83 0-002d: sn65dsi83_brg_start_stream

[ 44.961439] sn65dsi83 0-002d: sn65dsi83_write: write reg 0xe5 data 0xff

[ 44.992377] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x0d data 0x01

[ 45.204454] sn65dsi83 0-002d: sn65dsi83_write: write reg 0x09 data 0x01

[ 45.211166] sn65dsi83 0-002d: sn65dsi83_read client 0xfffffff00d748a80

[ 45.218146] sn65dsi83 0-002d: sn65dsi83_read: read reg 0xe5 data 0x81

[ 45.224682] sn65dsi83 0-002d: CHA (0xe5) = 0x81

console:/ #

Thank you,

Prathibha