Part Number: DS90LV011A

Other Parts Discussed in Thread: DS90LV012A, DS90LV011-12AEVM

Tool/software:

Dear TI team:

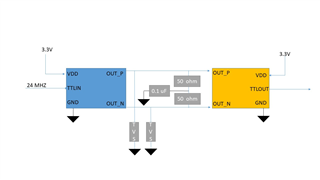

We had a project used the DS90LV011A+DS90LV012A for input a 24M HZ CLK.

DS90LV011A design as blew. But we found the screen will flick when device on.

Had try add 47pF to GND and series 56 ohm in TTL IN pin.

Issue had been improved but not completely resolved.

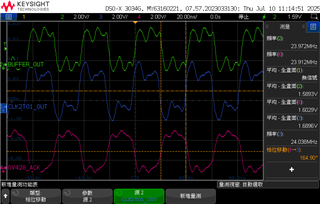

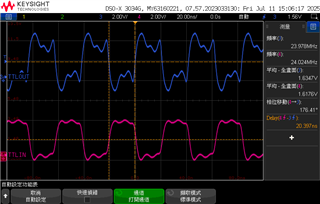

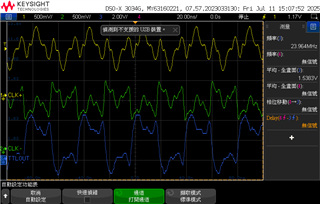

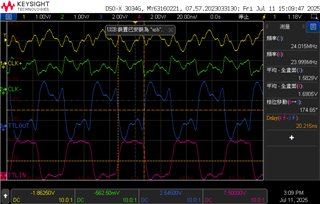

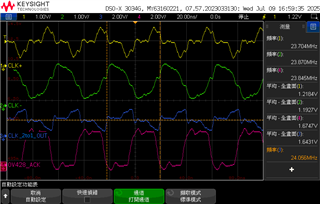

The TTLIN 、 OUT+/-、TTLOUT waveform as blew.

Seem TTLOUT have been attenuated.

Please help these question~

1.How can I fix this problem?

2.Is DS90LV011A can adjust the driving?

3.How far can TTLIN +OUT/- + TTLOUT be in total?

(Use DS90LV011-12AEVM to do experiment. It had same problem.)

Thanks~

Best Regards,

Andy