Part Number: THVD8000

Tool/software:

Hi Experts,

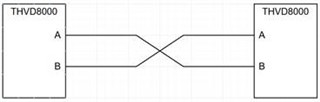

We want to use the THVD8000 in a project. It would simplify the layout if we could cross-connect the differential pins "A" and "B" on the two bus nodes. like this:

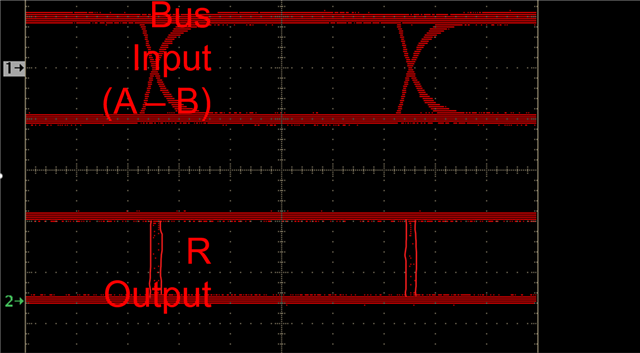

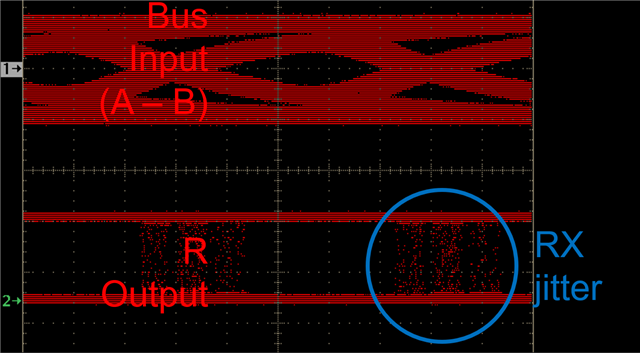

According to the data sheet, the "pulse-width distortion" deteriorates. However, I cannot fully explain what this means. What does this degradation of the "pulse-width distortion" mean?

Can you advise on this, please?

Regards