Tool/software:

Hello,

we used DP83867CRRGZ but sometimes connection falls down, let's say in random terms.

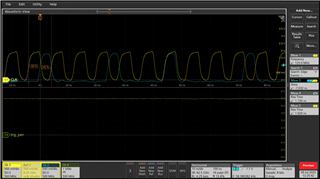

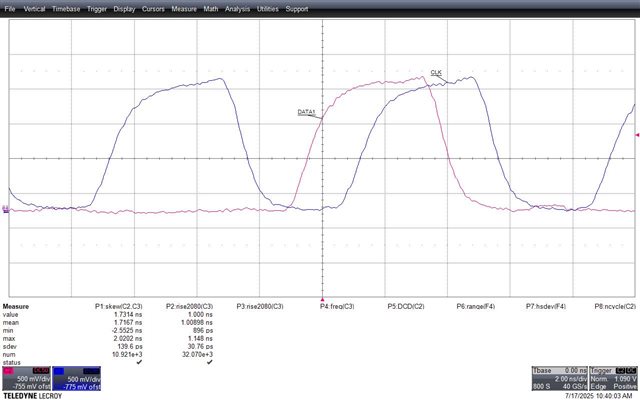

Firstly, we checked RGMII CLK and Data by oscilloscope and Z0 probes soldered at TX side wires near to the DP83867CRRGZ. Is it possible have good measuring results by this method?

CLK and Data signals are length matched on our PCB - pico seconds difference.

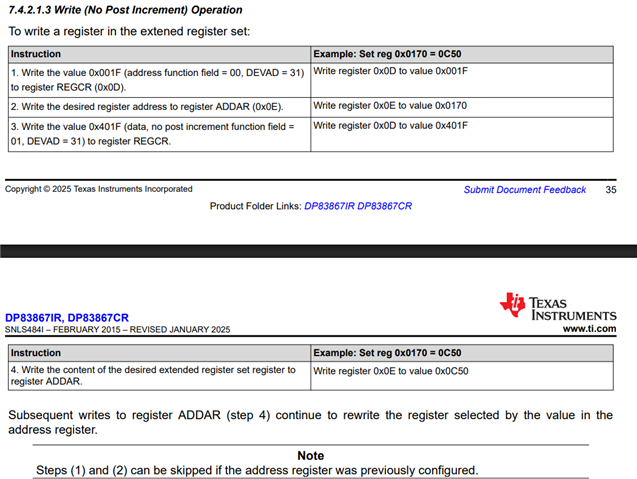

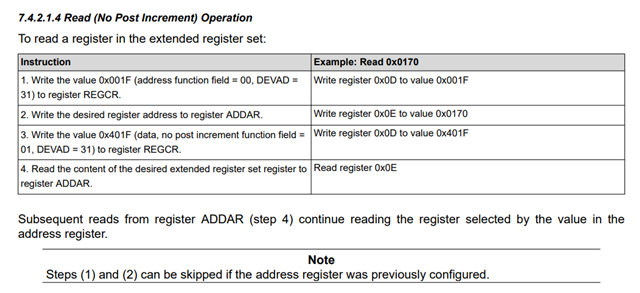

I guess the signal bellow is wrong and we need to properly set delays by 0x0086 register, but I'm not sure and I would be glad for another check to this issue.

The blue wave is CLK, and red Data signal.

Thank you so much for any idea how to solve our problem.

Tomas