Tool/software:

Hello, I see that a RF0N bit exists in both the MCAN Interrupts (address = h0824) and Interrupt Register (address = h1050) registers. What is the difference between the two? Do both need to be cleared (set to 1) after Acknowledging FIFO 0? I am using a driver that was supplied by TI and it does not include the h0824 register in the register map. I know this driver may not be perfect but it still concerns me.

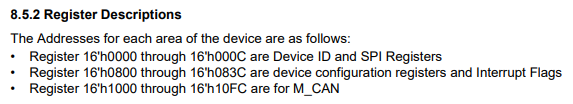

Can someone please help me to decode the below paragraph about h0824 from the datasheet?

"8.6.3 Interrupt/Diagnostic Flag and Enable Flag Registers: 16'h0820/0824 and 16'h0830

This register block provides all the interrupt flags for the device. As the M-CAN interrupt flags 16'h0824 are described in 16'h1050 MCAN register description section and will be shown here but need to go to 16'h1050 for description. 16h’0830 is Interrupt enable to trigger an interrupt for 16'h0820."

Thank you!

-Mike