Part Number: SN65DP159

Tool/software:

Hi Team,

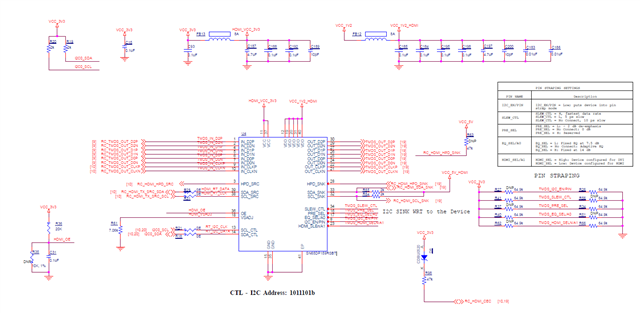

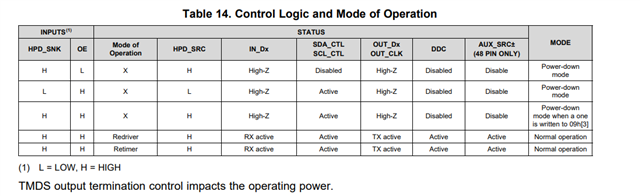

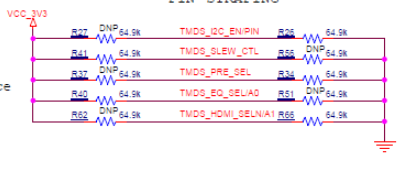

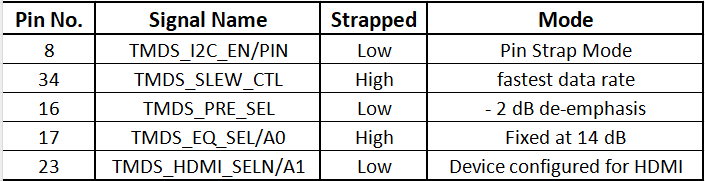

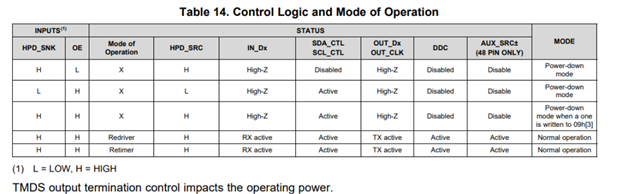

I am using SN65DP159RSBT in retimer mode for my HDMI 2.0 Tx application

Here, I am facing an EDID issue where the source is unable to read the EDID correctly and then proceeds to return an assumed value

This happens only when the monitor goes to sleep mode.

But when the monitor is not in standby/sleep mode for about 5-10 secs (where it displays no signal) and then we the source attempts to read an EDID, it will provide the details correctly

1. Is there something settings that should keep the monitor awake so as to read it whenever required

2. Should the retimer be responsible to keep the monitor awake?

3. Can it be possible that Monitor should send the EDID to source even when it is in Standby/sleep mode, but the retimer is not able to?

4. What is the purpose of DDC clock stretching here? Can i implement this? As i am confused due to the note on voltage levels that can be different on source and sink side (source is 3V3 and sink is 5V)

Based on the previous queries, we have one more setup (same setup and configuration) on which there is no toggling on the DDC lines at the sink side, we tried to give reflow multiple times but there is no improvement. Seems like the DDC Block is inactive.

For both the setup, OE pin is been provided with 2ms delay through an RC circuit since the 1V2 VDD will be arriving at 1.4ms while the 3V3 will be at instance 0ms.

Attached is the schematics, please let me know if any other details is required.

Regards,

M Karthik