Other Parts Discussed in Thread: USB2ANY, , LSF0102

Tool/software:

Hi TI Expert,

We are currently developing a development tool, a product similar to USB2ANY. The aim is to provide a solution capable of delivering a wide range of I2C voltages (1.2V to 5V) to a remote DUT (Device Under Test), while maintaining specific MCU-side I/O voltages for two I2C channels:

-

First I2C Channel:

- Operating in Fast Mode+ (up to 1 MHz).

- MCU-side I/O voltage: 3.3V.

-

Second I2C Channel:

- Operating in High-Speed Mode (3.4 MHz).

- MCU-side I/O voltage: 1.8V.

We are looking for a voltage level translator that can fulfill these requirements. Ideally, both I2C channel voltage level translators should support a wide range of voltages (1.2V to 5V) at the targeted operating frequencies for the remote DUT.

If it is not possible for both voltage level translators to support the full 1.2V to 5V range, we are open to alternative solutions that meet the operating frequency and voltage requirements for each channel.

1st case we like to evaluate as below:

-

First I2C Channel:

- Operating in Fast Mode+ (up to 1 MHz).

- MCU-side I/O voltage: 3.3V.

- Remote DUT side voltage has to support from 1.2V to 3.3V as shown below image.

2nd case we like to evaluate as below:

-

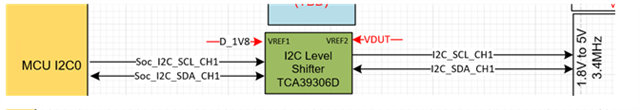

Second I2C Channel:

- Operating in High-Speed Mode (3.4 MHz).

- MCU-side I/O voltage: 1.8V.

- Remote DUT side voltage has to support from 1.8V to 5V as shown below image.

We are ok to enable and disable the pull-up resistor using below configuration:

we have some specific concerns regarding the voltage level translator for our I2C channels. We are seeking your guidance and recommendations to address the following:

-

Propagation Delay in HS-Mode:

When VREF1 equals VREF2, can the I2C voltage translator operate in HS-mode (3.4 Mbit/s) without concerns regarding propagation delay? If not, could you suggest an alternative solution that ensures reliable operation at this speed? -

VREF1 > VREF2 Scenario:

In our application, it is certain that VREF1 voltage will exceed VREF2 (VDUT varies between 1.2V and 5V). Are there any concerns or limitations in this scenario? If yes, what alternative solutions or configurations would you recommend? -

Enable Pin Biasing:

The EN pin must always be biased such that it does not exceed VREF_1 + Vth = VREF_1+ 0.6 V. However, in our use case, VDUT is expected to vary between 1.2V and 5V, and we are unsure how to drive the Enable pin appropriately. Could you provide guidance or suggest alternative solutions for this requirement?

We would greatly appreciate your input on suitable components, configurations, or design considerations to address these concerns.

Looking forward to your response

Best regards,

Vaibhav Kundariya