Part Number: DP83869EVM

Other Parts Discussed in Thread: DP83822IF, DP83869

Tool/software:

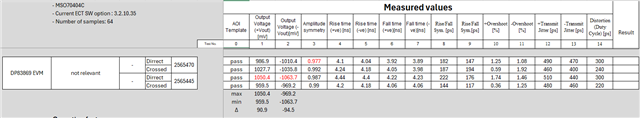

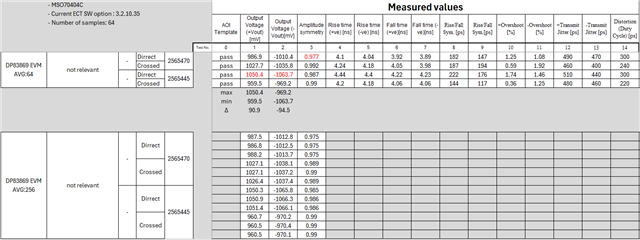

Hello, I have tow demo board with this PHY and I am facing that I measure at each piece different amplitude. the deviation is up to 90mV. Since the limit for ECT is in the range 100mV, this is much I would expect. Why there is such deviation. I did not found any information waht is distribution of the outptu amplitude. Can we get mote information about it?