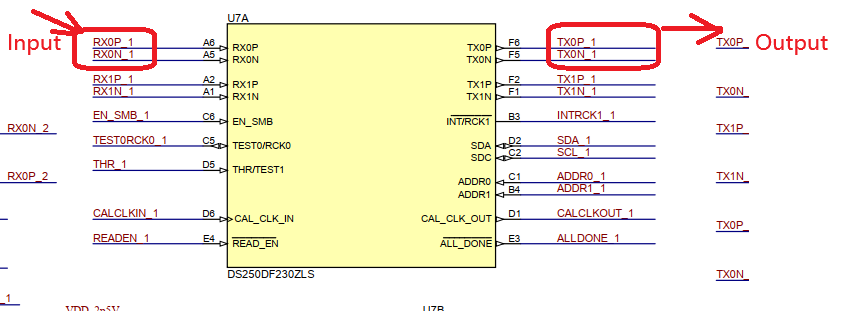

Part Number: DS250DF230EVM

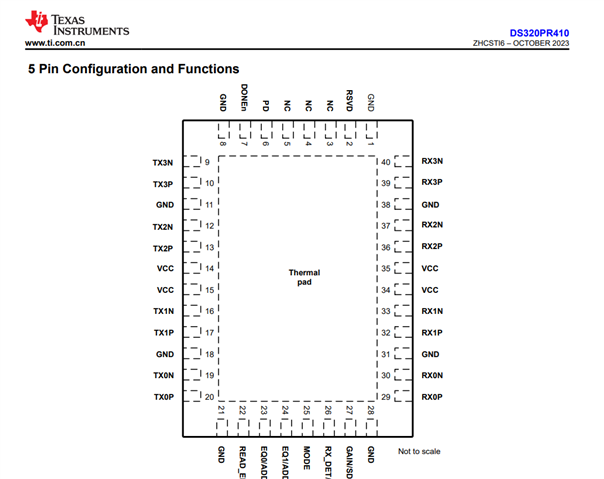

Other Parts Discussed in Thread: DS250DF230, DS320PR410

Tool/software:

Hi,

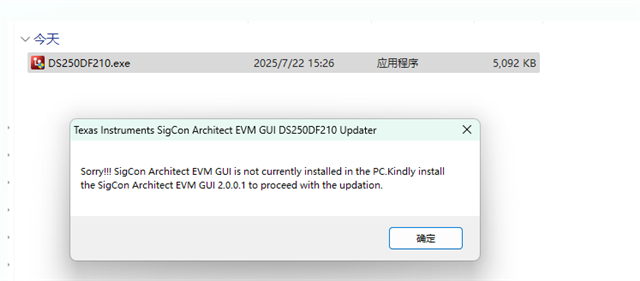

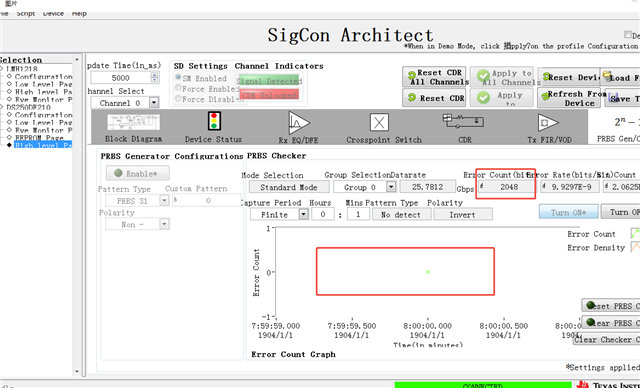

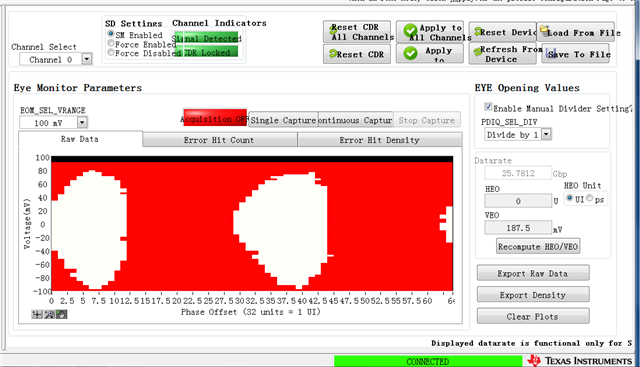

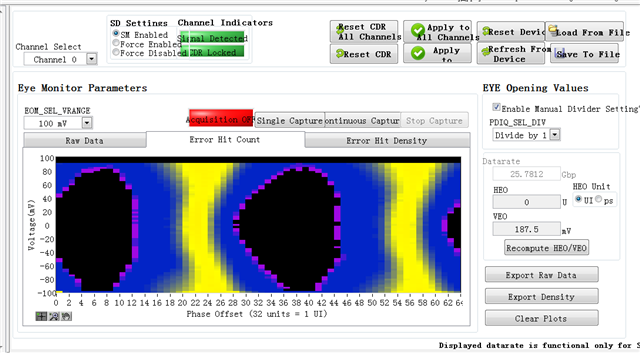

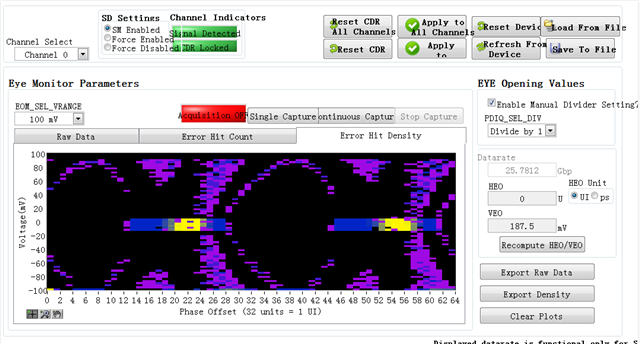

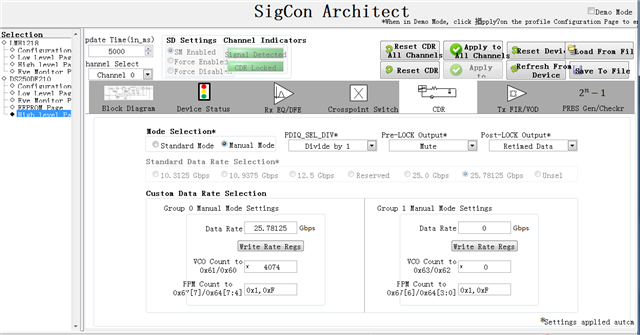

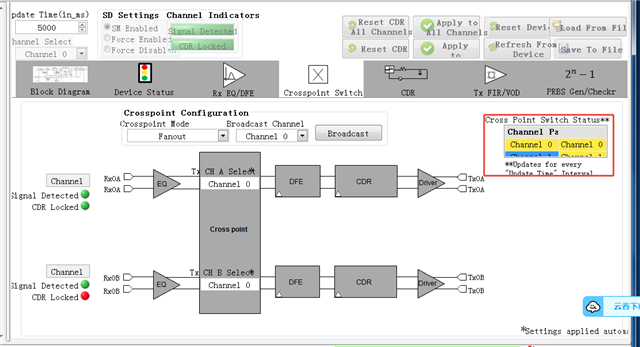

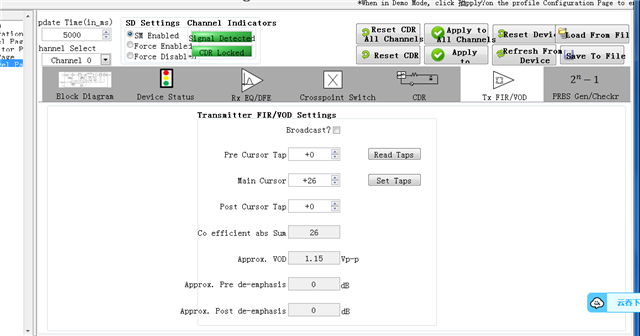

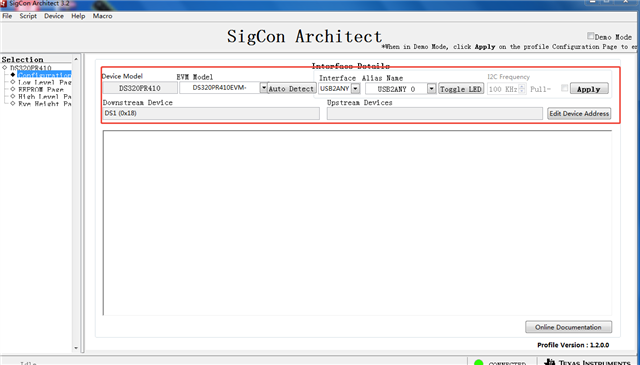

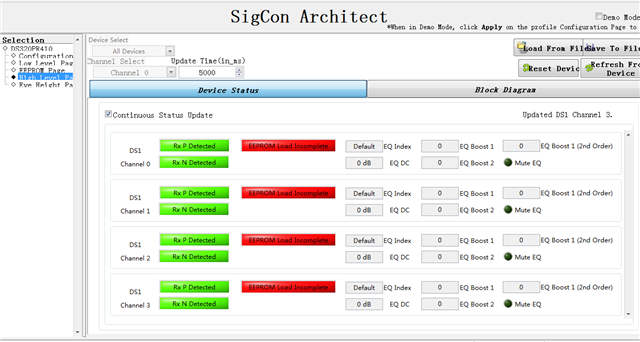

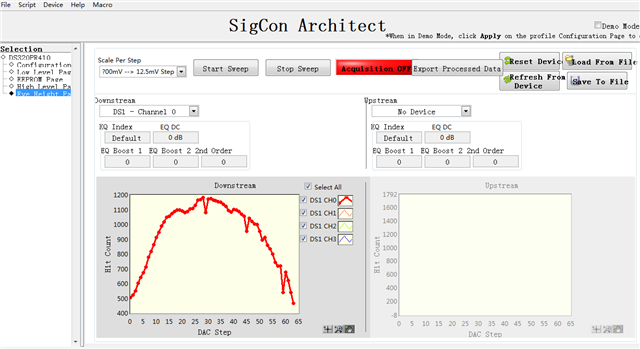

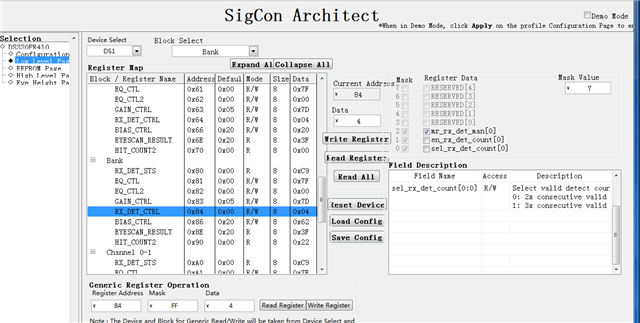

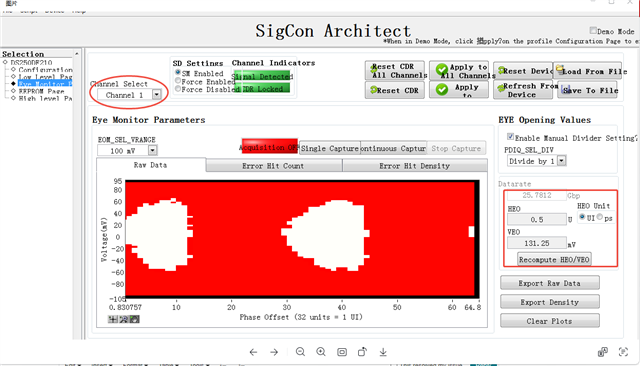

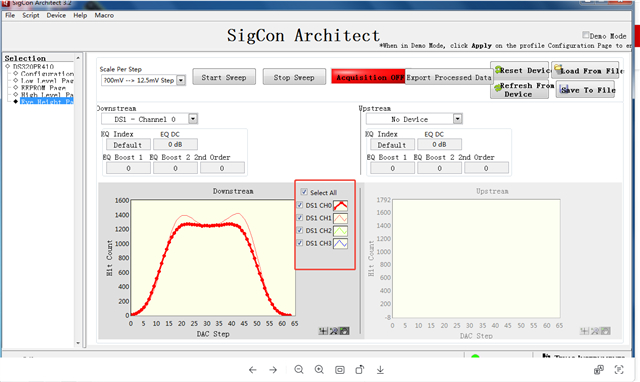

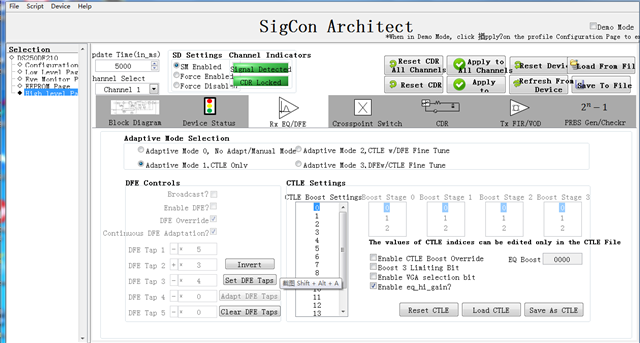

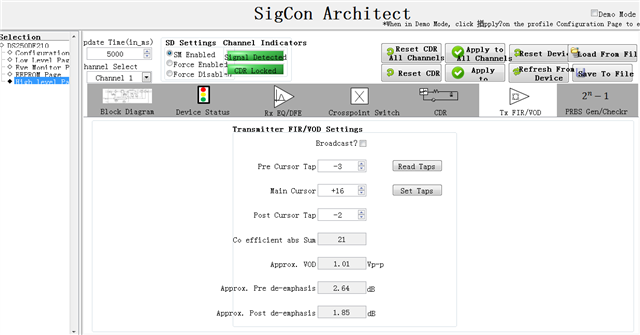

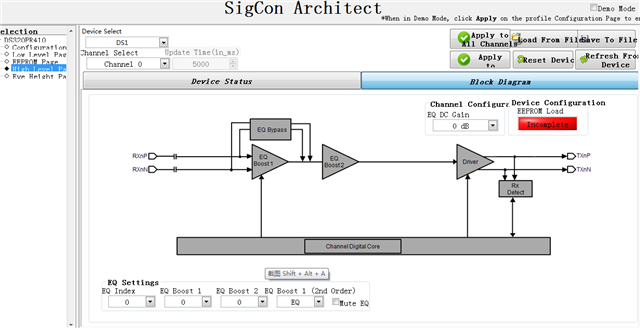

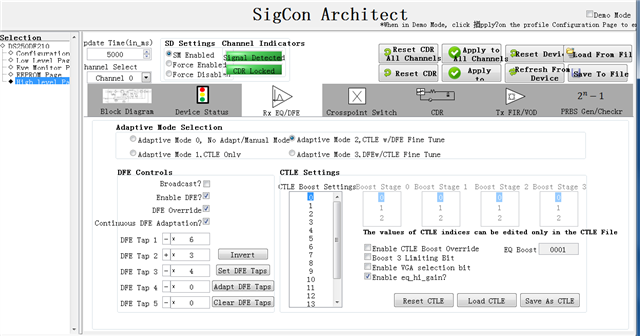

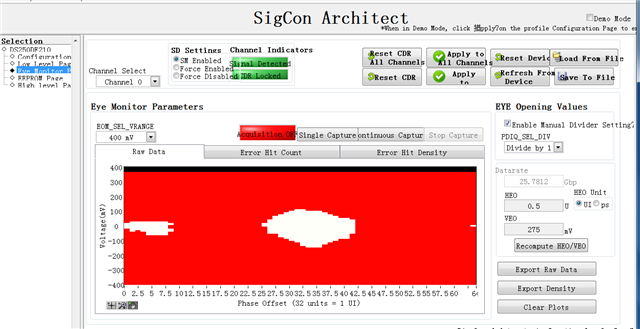

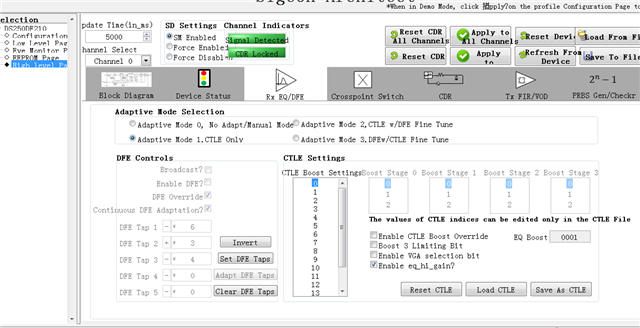

I want to use DS250DF230EVM, after download DS250DF230 device profile and install this program, it has information as below picture.

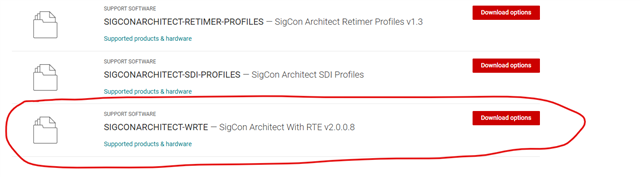

this device profile requeset SigCon Architecture EVM GUI 2.0.0.1, but the oldest software is 2.0.0.8 found in the TI Website, how can I use this software?

Many thanks.