Tool/software:

Dear Experts,

My customer is testing the voltage tolerance of VCC and VSUP and has found the following situations:

When a voltage of 13V is applied to VCC alone, it will cause damage to the VCC and VIO pins, resulting in VCC impedance to ground changing from ∞ to 20M Ω and VIO impedance to ground changing from ∞ to below 100 Ω

When a voltage of 70V is applied to VSUP alone, the impedance of VCC to ground changes from ∞ to 20M Ω, and the impedance of VIO pin to ground changes from ∞ to below 100 Ω

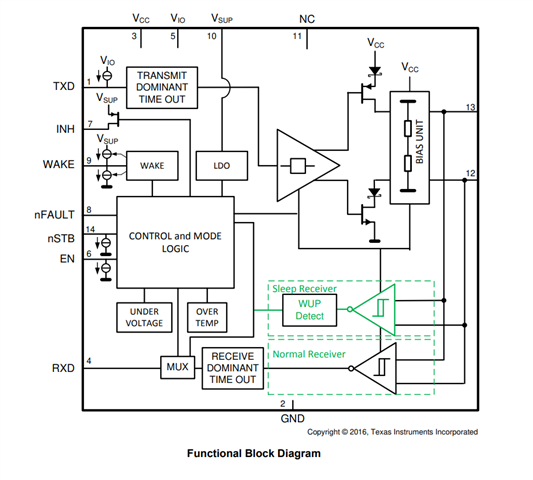

At present, we have seen the internal block diagram of TCAN1043-Q1 in the data manual, where the three pins are not connected together. We would like to know what the internal connections between these three pins are? Whether it is due to design reasons that may damage VIO when high voltage is applied. Thank you