Hi,

Does anyone have idea on the minimum separation for SCL and SDA traces of I2C?

It is very common for ICs using I2C protocol to have SCL and SDA pins next to each other, and at many times traces extending from the two pins are also parallel. However, on a really dense board where routing space is restricted strongly by other parts and existing routing, I was forced to route SCL and SDA traces close and in parallel with a separation of only 4mil, with widths of SCL and SDA both also being 4mil.

From EMI perspective, the larger the separation, generally the better the signal integrity. With SCL and SDA being so close, is there any possibility for crosstalk and other forms of interference?

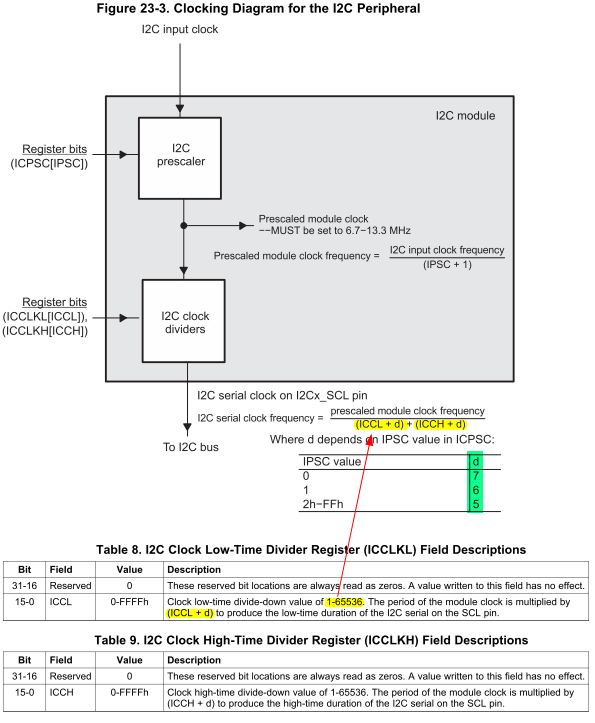

I2C has two modes: standard 100KHz and fast 400KHz. However, I believe I2C speed slower than standard mode can also be achieved since TI processor's I2C module has register bits ICCLKH[ICCH], ICCLKL[ICCL] which could be used to divide down I2C prescaler clock (which is required to be between [6.7, 13.3] MHz). Since the range of both is [0, 65536], considering maximum ICCLKH[ICCH] + ICCLKL[ICCL] = 217 = 128K, and assuming d=0 (see green highlight), then the lowest achievable I2Cx_SCL pin clock would be 7MHz (7-12MHz range) prescaler clock divides 217 = 7 × 220 / 217 = 7 × 23 = 56Hz, which is an extremely low speed for a digital communication.

Three questions:

1. Is this 56Hz clock actually attainable?

2. When clock speed goes down, wavelength would increase so that more and more the separation between tracks no longer causes problem. But how slow does the clock need to be for SCL and SDA to be free from interference/crosstalk, when separation = width(SCL) = width(SDA) = 4mil?

3. Is 4mil separation too small for I2C communication?

Tim