Part Number: SN65DSI84

Tool/software:

Dears,

My customer use SN65DSI84 for Single-Link LVDS,4 lane to driver LCD(1024x600),the attachment is LCD datasheet.Could you pls help offer a Register Configuration Table for this case? Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DSI84

Tool/software:

Dears,

My customer use SN65DSI84 for Single-Link LVDS,4 lane to driver LCD(1024x600),the attachment is LCD datasheet.Could you pls help offer a Register Configuration Table for this case? Thanks.

Hi Jon,

Could you please use the DSI Tuner Tool to generate the specifications as needed: SN65DSI83: DSI TUNER tool needed

Please use the link above to download.

And here is a step-by-step guide: [FAQ] SN65DSI84: How to configure the SN65DSI84 and SN65DSI85 for single channel DSI to dual channel LVDS

Best regards,

Ikram

Ikram,

The customer has already used this tool to generate register configurations, but the PLL cannot be locked. Unable to lock in Test Pattern mode. Could you pls help review this register configurations? Thanks.

{0x09, 0x00},

{0x0A, 0x03},

{0x0B, 0x10},

{0x0D, 0x00},

{0x10, 0x26},

{0x11, 0x00},

{0x12, 0x1e},

{0x13, 0x00},

{0x18, 0x78},

{0x19, 0x00},

{0x1A, 0x03},

{0x1B, 0x00},

{0x20, 0x00},

{0x21, 0x04},

{0x22, 0x00},

{0x23, 0x00},

{0x24, 0x00},//pattern

{0x25, 0x00},//pattern

{0x24, 0x58},//pattern

{0x25, 0x02},//pattern

{0x26, 0x00},

{0x27, 0x00},

{0x28, 0x21},

{0x29, 0x00},

{0x2A, 0x00},

{0x2B, 0x00},

{0x2C, 0x40},

{0x2D, 0x00},

{0x2E, 0x00},

{0x2F, 0x00},

{0x30, 0x0a},

{0x31, 0x00},

{0x32, 0x00},

{0x33, 0x00},

{0x34, 0xa0},

{0x35, 0x00},

{0x36, 0x00},//pattern

{0x36, 0x17},//pattern

{0x37, 0x00},

{0x38, 0x00},//pattern

{0x38, 0xa0},//pattern

{0x39, 0x00},

{0x3A, 0x00},//pattern

{0x3A, 0x0c},//pattern

{0x3B, 0x00},

{0xE0,0x01},

{0xE1,0xff},

// Enable test pattern mode: Color Bars

{0x3C, 0x10}, // Set test pattern type: 0x0A = Color Bars

};

Hi Jon, thank you for sharing this. I will check with the tool and get back to you by tomorrow.

Best regards,

Ikram

Hi Jon,

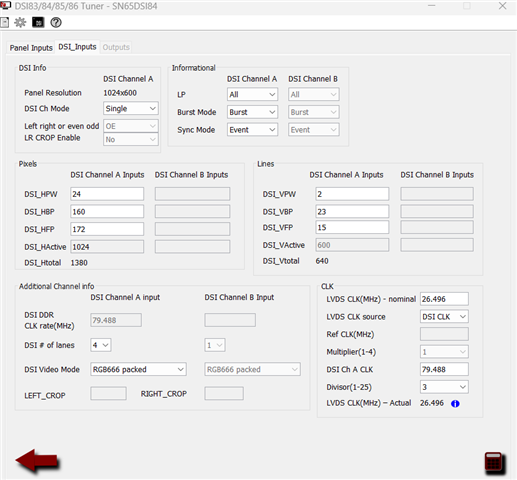

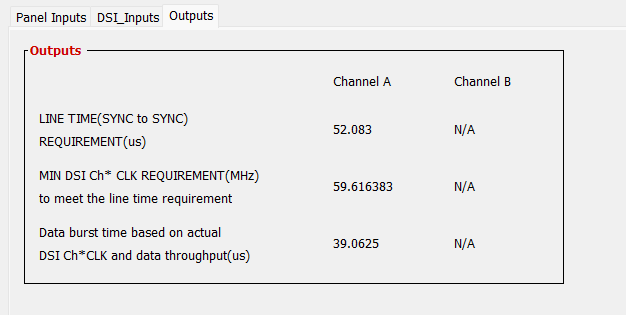

You can use the DSI Tuner tool to enter the resolutions that are within the specifications of the display as you shared, and which the SoC or DSI source will generate. Here are the settings I used:

Here is the Test pattern CSR register list it generated:

//===================================================================== // Filename : test_pattern_0801.txt // // (C) Copyright 2013 by Texas Instruments Incorporated. // All rights reserved. // //===================================================================== 0x09 0x00 0x0A 0x01 0x0B 0x10 0x0D 0x00 0x10 0x26 0x11 0x00 0x12 0x0f 0x13 0x00 0x18 0x70 0x19 0x00 0x1A 0x03 0x1B 0x00 0x20 0x00 0x21 0x04 0x22 0x00 0x23 0x00 0x24 0x58 0x25 0x02 0x26 0x00 0x27 0x00 0x28 0x20 0x29 0x00 0x2A 0x00 0x2B 0x00 0x2C 0x18 0x2D 0x00 0x2E 0x00 0x2F 0x00 0x30 0x02 0x31 0x00 0x32 0x00 0x33 0x00 0x34 0xa0 0x35 0x00 0x36 0x17 0x37 0x00 0x38 0xac 0x39 0x00 0x3A 0x0f 0x3B 0x00 0x3C 0x10 0x3D 0x00 0x3E 0x00 The PLL_EN bit and SOFT_RESET bit are not set as they need to be set per the recommended sequence defined in the datasheet

//===================================================================== // Filename : DSI_input_0801.txt // // (C) Copyright 2013 by Texas Instruments Incorporated. // All rights reserved. // //===================================================================== 0x09 0x00 0x0A 0x01 0x0B 0x10 0x0D 0x00 0x10 0x26 0x11 0x00 0x12 0x0f 0x13 0x00 0x18 0x70 0x19 0x00 0x1A 0x03 0x1B 0x00 0x20 0x00 0x21 0x04 0x22 0x00 0x23 0x00 0x24 0x00 0x25 0x00 0x26 0x00 0x27 0x00 0x28 0x20 0x29 0x00 0x2A 0x00 0x2B 0x00 0x2C 0x18 0x2D 0x00 0x2E 0x00 0x2F 0x00 0x30 0x02 0x31 0x00 0x32 0x00 0x33 0x00 0x34 0xa0 0x35 0x00 0x36 0x00 0x37 0x00 0x38 0x00 0x39 0x00 0x3A 0x00 0x3B 0x00 0x3C 0x00 0x3D 0x00 0x3E 0x00 The PLL_EN bit and SOFT_RESET bit are not set as they need to be set per the recommended sequence defined in the datasheet