Tool/software:

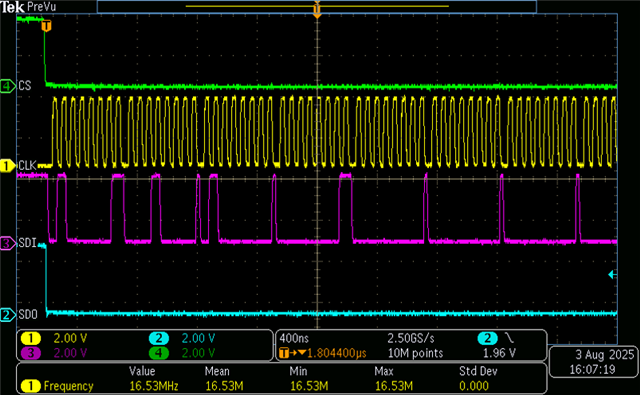

I am observing an unusual signal behavior in my waveforms, and I would appreciate some clarification.

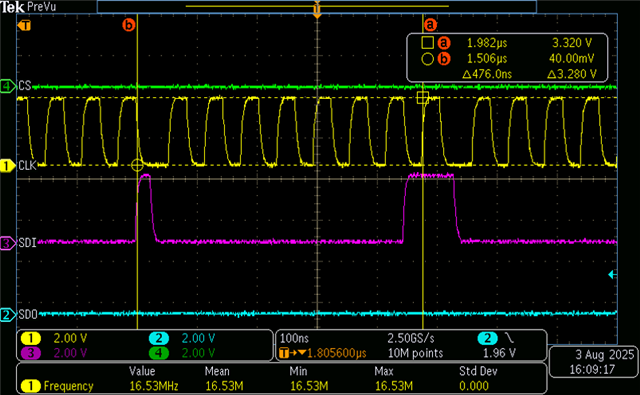

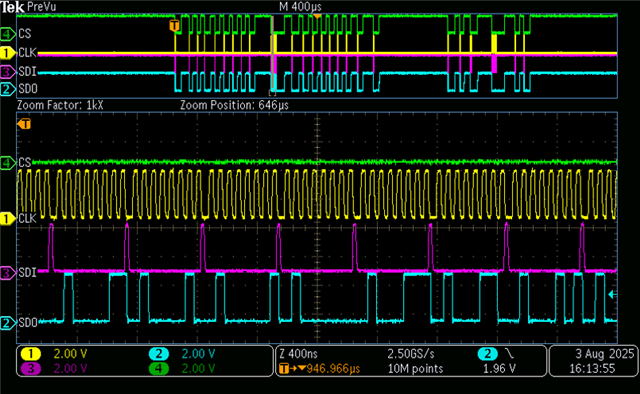

In the attached oscilloscope images, you can see that after each word transmission, when the clock momentarily halts before the next word starts, a brief spike appears on the SDI line. This spike lasts for a duration shorter than one bit period.

On the surface, this shouldn't be a problem, as the "bit" is not sampled because SDI is sampled on the rising edge according to the DS. In the second image, you can also see that this spike occurs while the clock is low, so it seems like it wouldn't be sampled/

Could you confirm whether this is expected behavior, or if there might be a potential issue with signal integrity or timing?

Thank you for your assistance!