Tool/software:

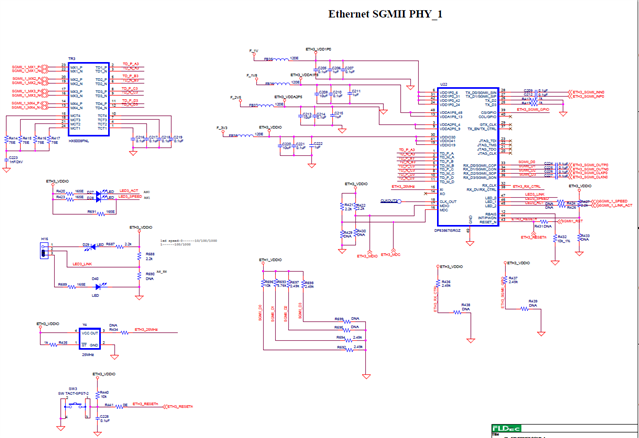

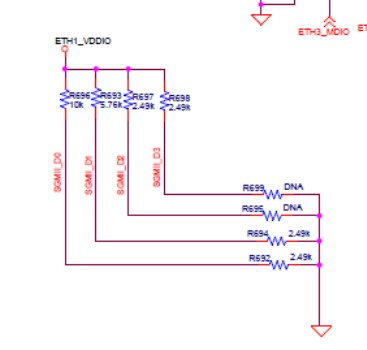

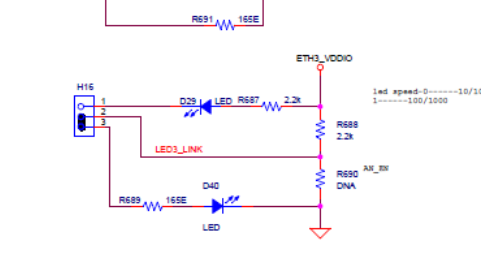

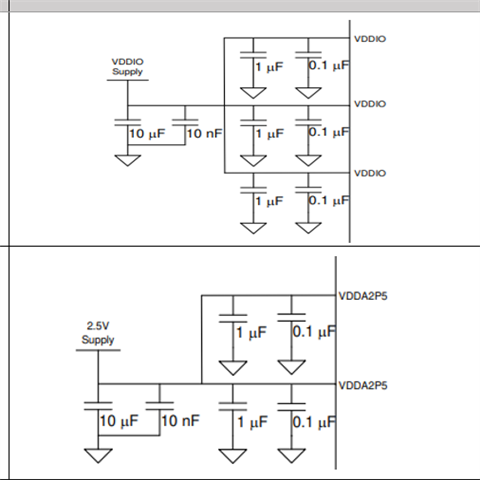

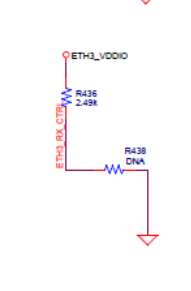

We are using DP83867ISRGZT PHY chip for SGMII interface with Zync MPsoc IC, We are able to linkup and communicate the PHY chip IC but sometimes randomly linkup and communication is not happening , So kindly suggest the solution for sort outing this problem.