Part Number: TXB0104

Other Parts Discussed in Thread: LSF0204, TXU0304, TXU0104, TXU0204

Tool/software:

Hi,

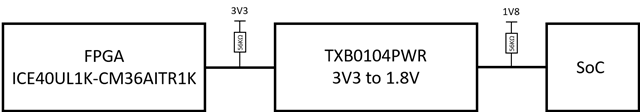

I'm using the level translator part TXB0104PWR in my design to interface an FPGA (3.3V) with a SoC (1.8V).

Here’s the setup:

- The FPGA outputs a RESET signal which is open-drain and is pulled up to 3.3V using a 56kΩ resistor.

- This RESET signal is connected to the 3.3V side of the level translator (VCCB).

- The 1.8V side (VCCA) of the level translator connects to the SoC and is also pulled up to 1.8V via a 56kΩ resistor.

- The FPGA has been programmed in such a way that it always stays at 3.3V, which power on the SoC

- When the FPGA drives LOW, the SoC is held in reset and will power off.

I’ve confirmed both the FPGA and SoC are functioning correctly in isolation. However, the RESET logic fails to operate as expected in the system, and the SoC doesn’t come out of reset. This points toward a potential issue with the level translator behavior in this open-drain setup. Is the level translator has been used in the correct configuration? Please let me know if any additional configuration requirements or constraints to be aware of in such open-drain driven circuits.