Part Number: TCAN4550EVM

Other Parts Discussed in Thread: TCAN4550

Tool/software:

I have a question about the TCAN4550EVM.

I'm connecting a Raspberry Pi and a TCAN4550 EVM via an SPI interface.

My goal is to measure the CAN frame data transmitted from the Raspberry Pi through the TCAN4550's CAN Bus DB-9 Wiring Harness Connector.

I've created a program based on the TCAN4550 sample program, intending to transmit data from the TCAN4550's TxBuffer, but haven't been successful.

I can read and write to the TCAN4550 EVM registers from the Raspberry Pi.

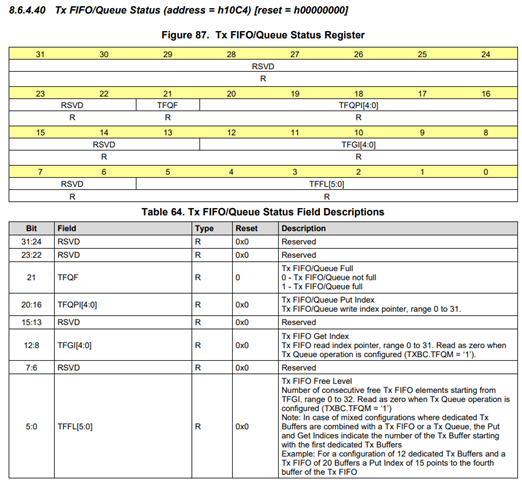

I'm writing to the SPI according to the TCAN4550 software user manual, but I seem to be unable to retrieve the free level from register 0x10C4; the value I'm getting is 0.

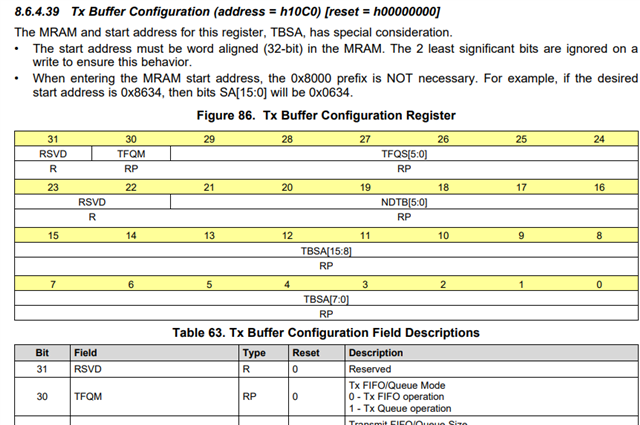

According to the datasheet, this is caused by the Tx being configured as a queue (register TXBC.TFQM = ‘1’).

Reading TXBC using AHB_READ_32() returned 0x4a000174. Since 0x4a000174 indicates TXBC.TFQM=1, I believe the Tx is configured as a queue.

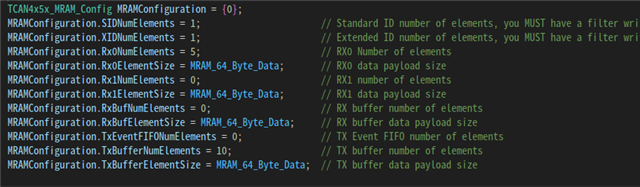

The MRAM configuration appears to be set using TCAN4x5x_MRAM_Configure(), but I couldn't find a way to configure the Tx as a FIFO in the sample program.

How can I configure the Tx to operate as a FIFO?