Dear Community:

I need to access Memory-Mapped TI Proprietary Register Space of XIO2000A. How do I find the base address where those registers are mapped to?

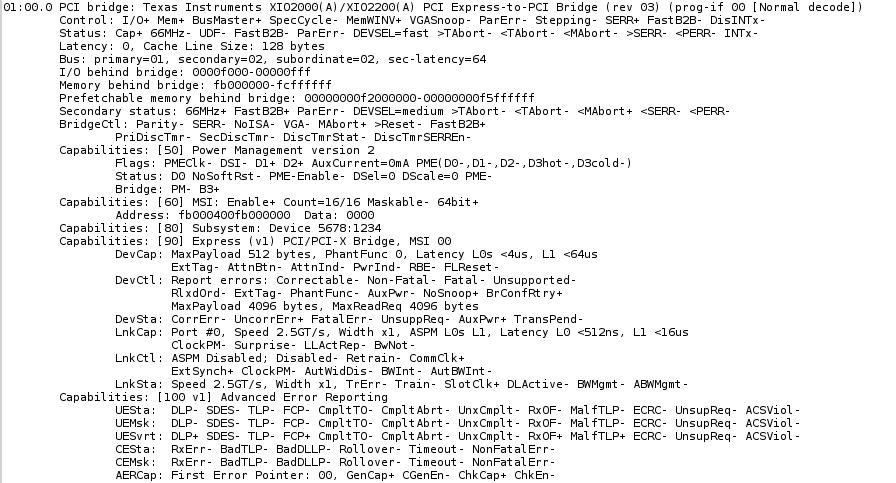

lspci -vvv gives me:

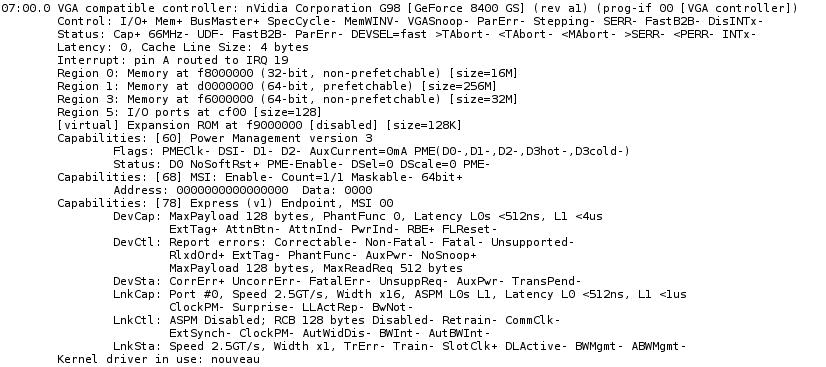

PCI Device behind the bridge:

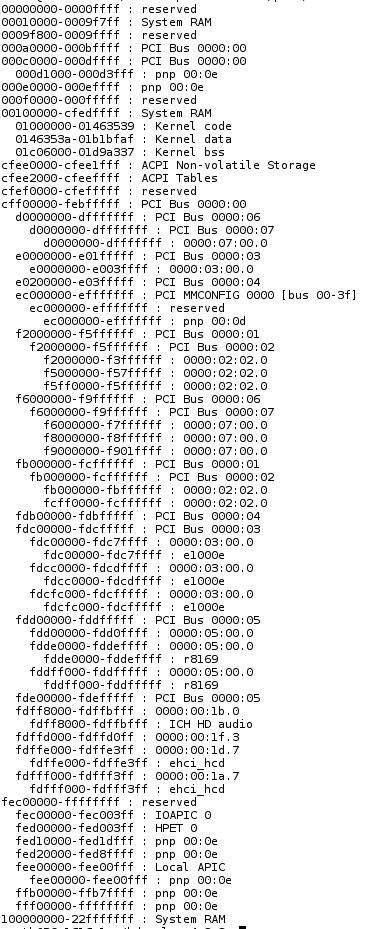

cat /proc/iomem gives me:

My OS is Linux with kernel version 2.6.34-12.

Thank you for your reply.

Alexander