Tool/software:

hello support,

we faced a strange case in DP83TC811R-Q1 PHY,

after PHY bootup ( control by reset pin), no signal output from CLKOUT pin,

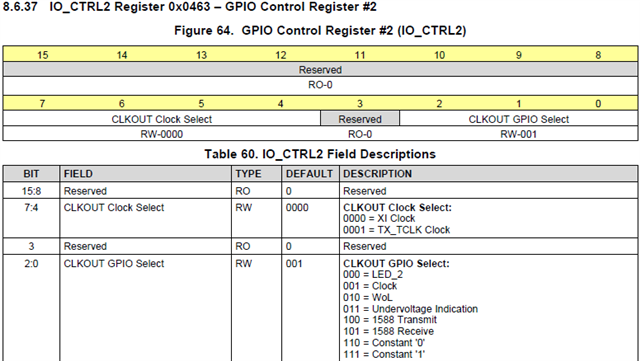

only after set register 0x0463 with 0x0001, the clock signal can be read from CLKOUT pin

beaed on your Datasheet, that register default value is 0x0001,

I have doubts, why need set the register with default value to trigger output XI clock? is the PHY default value not effective?