Tool/software:

Hi team,

Tier 1:Neusoft

OEM: Geely

During a cold restart of the host, the DSI84 displays normal graphics, and the 0xe5 fault status register is normal.

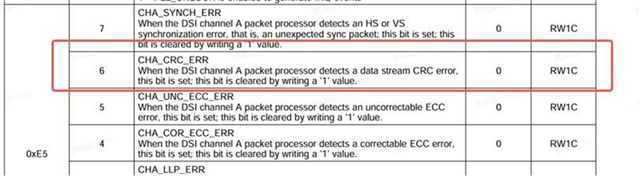

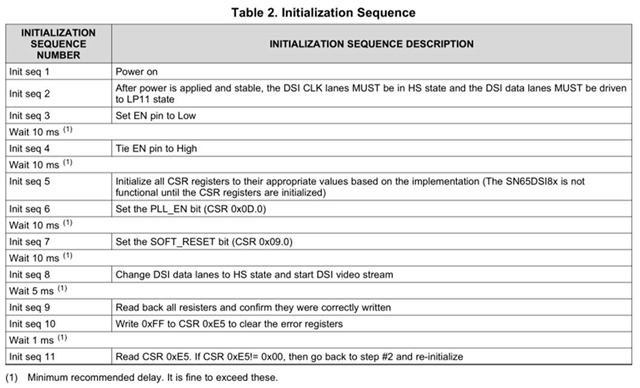

When the STR is released, the DSI84 image displays normally, but bit 6 of the 0xe5 fault status register is 1, and a CRC error is reported. (I have executed Write 0xFF to CSR 0xE5 to clear the error registers, but it does not clear the error.)

Please provide feedback tomorrow morning on the following issues:

1. If bit 6 is reported as an error, what impact will it have on the graphics?

2. Please provide some troubleshooting advice.

The attached pictures are the DSI84 initialization waveforms during cold start and STR escape. The timing is designed according to the following requirements;

Cold start (blue reset, pink dsi data, yellow I2C)

STR escape (blue reset, pink dsi data, yellow I2C) (STR (Suspend to RAM) is a low power mode)

Blue EN, green DSI DATA, pink DSI CLK1 --- cold start