Other Parts Discussed in Thread: AM625

Tool/software:

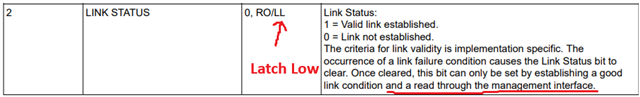

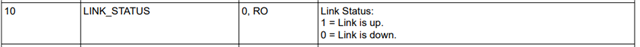

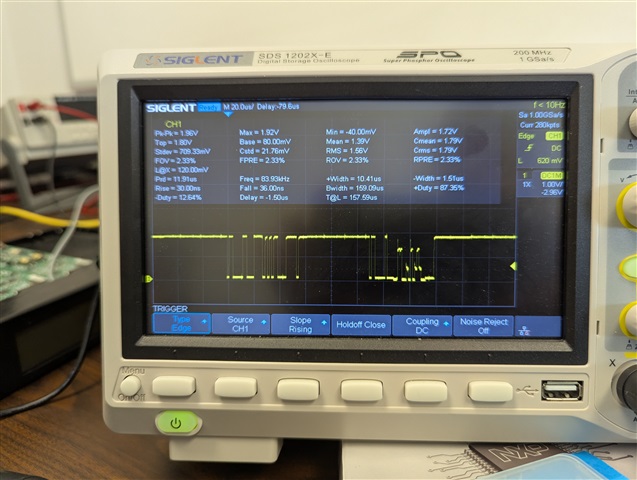

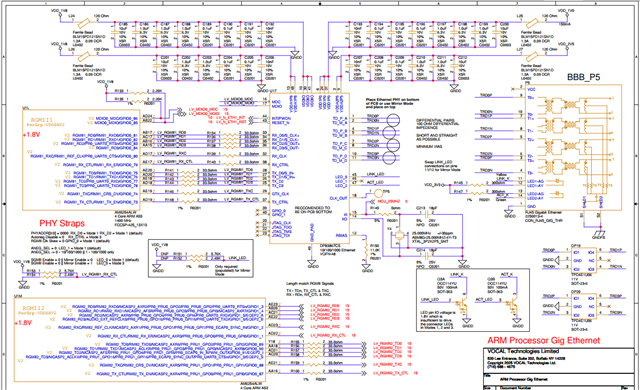

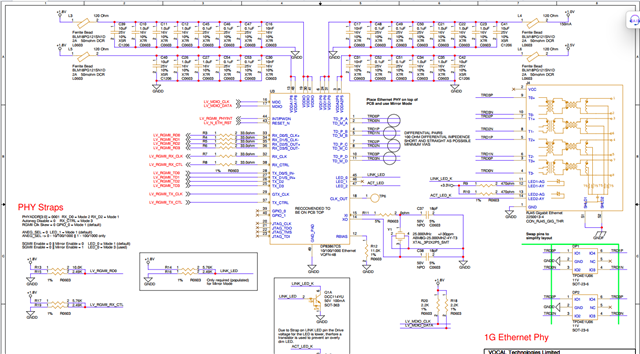

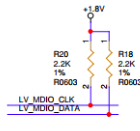

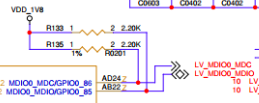

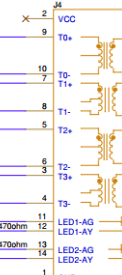

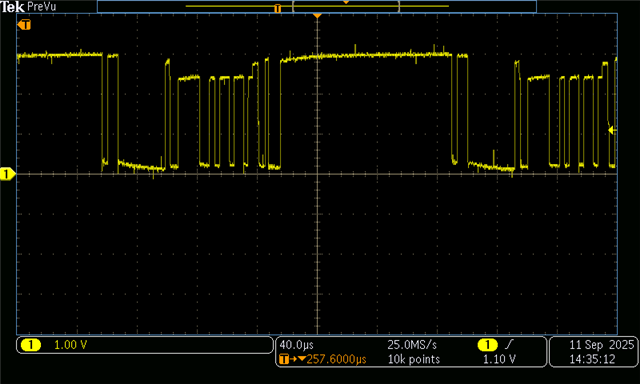

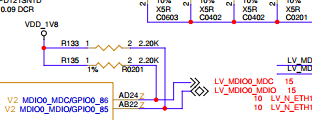

We are finding that the link status of the DP83867CS is not being read reliably over the MDIO. Our new board, Beagle Violet uses an AM625 host processor running Linux. By default, the MDIO is using bit-banging (not hardware). This choice may have been due to an early implementation of the AM625 on a BeaglePlay with a different (non-TI) PHY. Is there any know reason to use the bit-bang MDIO with this TI PHY? Any experience with unreliable link status?

We sort of avoid this problem by reading the PHY status twice when the link appears to be going from UP to DOWN. This improved our reliability greatly (but its a change to a Linux driver that we would like to avoid). We also noticed false DOWN to UP readings on a second ethernet port which was left unconnected.