Part Number: DP83867CS

Tool/software:

Hello,

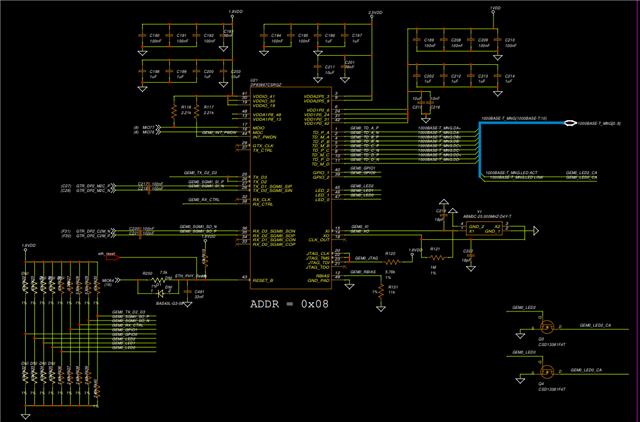

My team designed a board with three Ethernet connections, which means it includes three PHY components DP83867, all connected to the same MDIO lines but with different addresses (4, 8, 12).

In addition, the board has a processor running a linux operating system that communicates with the components on the board.

When the board is powered on, all three Ethernet ports communicate successfully, but after several hours of operation, one of the ports stops communicating and the operating system outputs the message:

After this happens, it is no longer possible to access the PHY via the MDIO lines.

Could you help us figure out how to prevent this issue?

Note – On the same board we designed, there is another processor with an linux operating system,with two PHY components are connected (i.e., two Ethernet ports) that share the same I2C MDIO line but have different addresses (4 ,8), and in that case we do not encounter this problem at all.