Part Number: DS100MB203

Other Parts Discussed in Thread: DS280DF810, DS250DF230, DS560DF810

Tool/software:

Gooday,

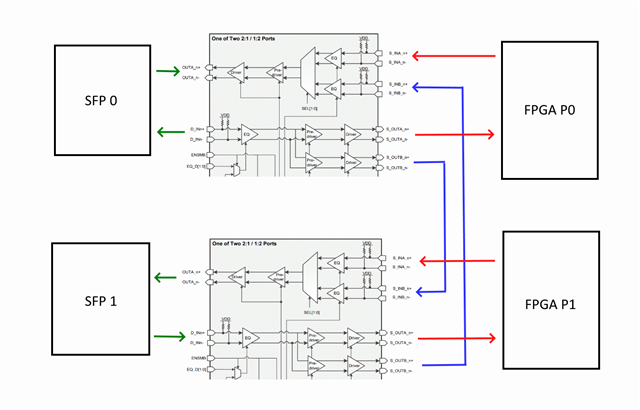

I have a design that uses the DS100MB203 between a FPGA host and 2 10GBASE-T1 PHYs where the SERDES is configured as 10GBASE-R.

/cfs-file/__key/communityserver-discussions-components-files/138/1108.UMAR_2D00_10G02.pdf

There is a passive MUX between the DS100MB203 and the PHYs/SFP ports, which are used to select which end point to use.

In PHY mode (PHYTX/RX) the interface works at full speed from the FPGA to the PHY, however packets are lost and have errors when traveling from the PHY to the FPGA through the DS100MB203.

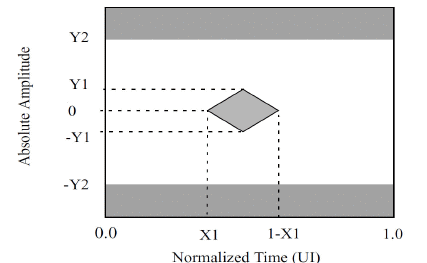

Above is a picture of the transmitter eye mask of the PHY.

Y1 and Y2 are minimum 170mV and maximum 425mV respectively.

Can you suggest what settings the MUX should have or is there anything in the design I may have missed?

Notes:

I have tinkered with the I2C registers in the MUX for CH4 (D_IN0 – S_OUTA0) which is one of these receive paths. Changing the EQ or DEM registers above 0 seems to stop the traffic all together and the VOD and RXDET registers seem to have no affect.

Also, when I place my finger on the SERDES traces, this seems to reduce the number of errors, and in some cases remove them all together. Maybe this points to something.

Any help would be much appreciated.

Thank you