Tool/software:

Dear TI Team,

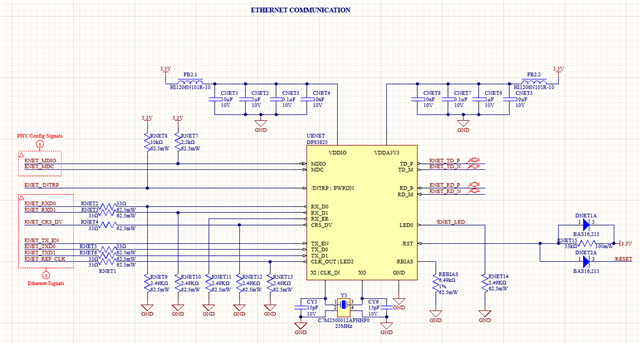

We are using a STM32H757 microcontroller with the DP83825I phy (linked together through the RMII interface) where the phy is linked to a 25MHz quartz to be able to give a 50MHz reference clock to the CPU. Some communication losses happened when an ethernet cable is plugged into the RJ45 connector (RJ45 with integrated magnetics). We checked the MDIO + MDC signals and RX0-1/TX0-1 signals with the reference clock given by the phy and everything seems to be ok (compared with an other circuit with the phy linked to a LPC54606 microcontroller from NXP which works correctly).

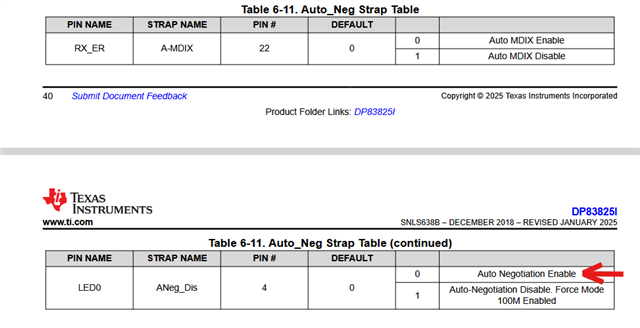

However, when we checked the registers configurations, we noticed that some registers (LEDCR, MLEDCR and PHYSTS for example) which are not configured by our program did not have the default values inidcated by the datasheet. As consequences, the activitty LED (linked on the LED0 physical pin of the phy), has an inverted polarity "by default" (bit 7 of the LEDCR register is 1 by default instead of 0).

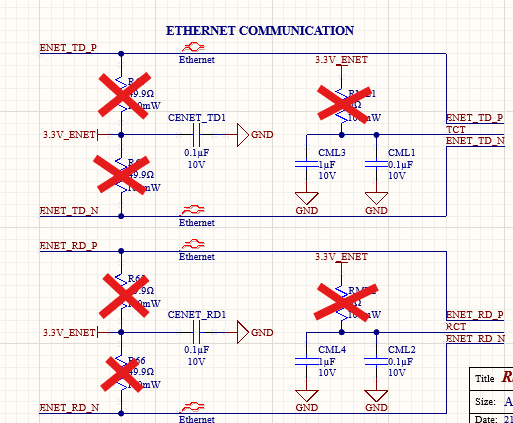

Please find in attachement, the schematics about the phy wiring :

(the crossed out components are not populated)

Thank you very much,

Best regards,

Benjamin