Tool/software:

Hello,

I'm trying to use a Pattern generator function in DS90UH948-Q1.

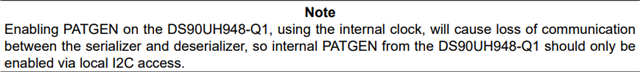

In that evaluation, beased on the NOTE in datasheet below,

NOTE: CML TX must be powered down prior to enabling Pattern Generator

I modified CML_OUTPUT_CTL3 Register from 0x00 to 0x01.

However, the deserializer changed Lock status output from low to high at the same time of command issued.

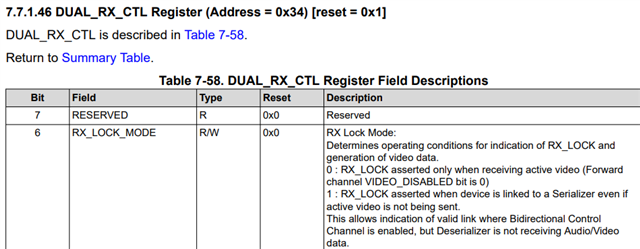

I would like to know the reason why the Lock Status became low output when CML TX powered down.

We also want to know how to keep lock status high even when we make CML TX powered down.

That's because when the low lock status is detected, the overall system of our product will attempt to power down all components, including the deserializer, preventing us from continuing the evaluation.