Tool/software:

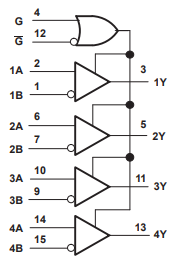

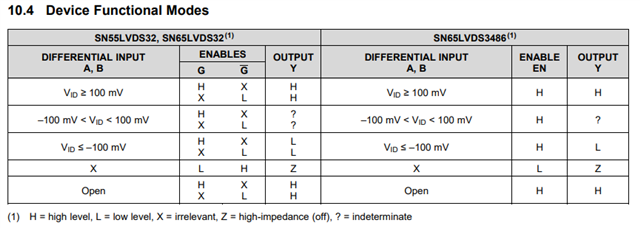

Hi, I am dealing with an issue on my design using the SN65LVDS32DR where driving the enable (active low) pin G̅ into a high state does not disable the chip outputs and set them to a high Z state.

My supply voltage is 3.3V and I have checked with a scope that 3.3V is present on the G̅ pin 12, but the outputs are still active, causing them to fight with another digital signal driver.

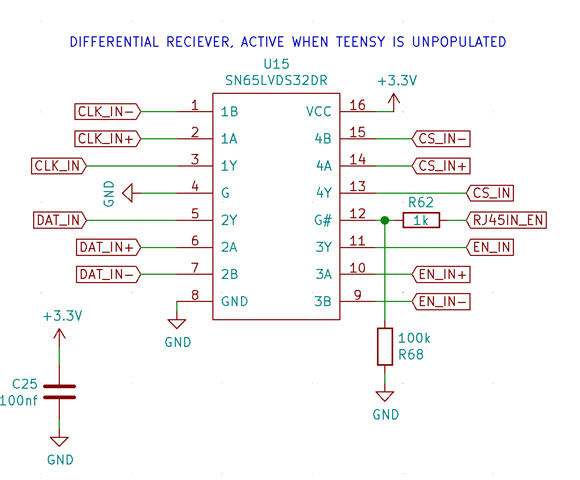

Here is the relevant portion of my schematic:

I write RJ45IN_EN high with a micro pin to disable the SN65LVDS32DR chip (so the micro can provide these signals instead) but even with the micro pin holding G# (pin 12) at 3.3V the outputs are still fighting with my micro output (shows up as voltage drop and noise). The issue does not go away until I physically remove the SN65LVDS32DR from the board.

Pleaes advise on what is going wrong here, this seems to directly contradict the behavior described in the datasheet.

Thanks!