Tool/software:

Hello. I am using TUSB1210 connected to Xilinx Zynq MPSoC.60MHz CLK is generated by TUSB1210.

I have 3 small questions, I would be grateful for any help.

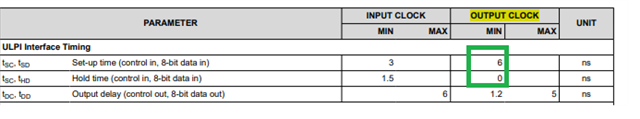

1. Are my setup and hold time measurements correct on screenshot below, ? I measure 11.92ns setup time and 4.8ns hold time.

Does it mean I am good with TUSB1210 timing spec? Setup time is defined as min. 6ns and hold time as min. 0ns.

(please ignore small, non-monotonic bumps on my data edges, I measured it on the wrong side of the trace (driver side))

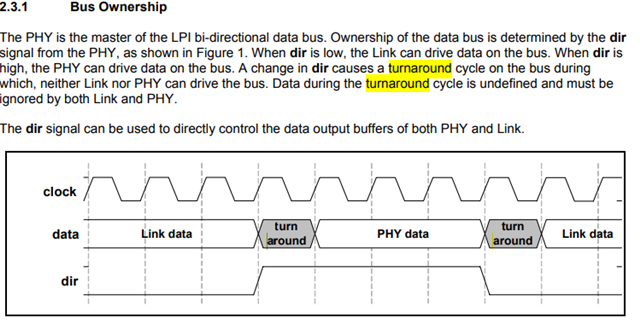

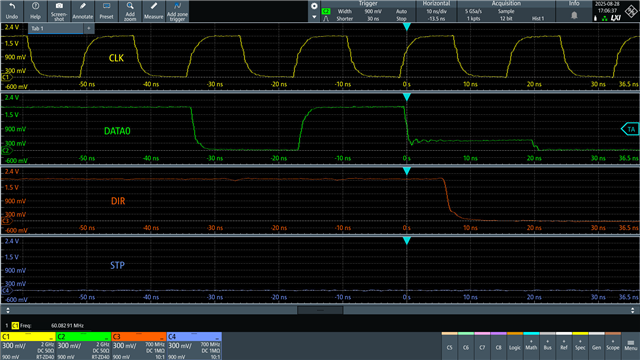

2. How to measure setup and hold time when DIR =1?

Xilinx spec is to have >4.5ns setup and >0ns hold time. Should I ignore the first CLK edge after DIR going high?

In my screenshot the one jest before 0s point.

3. I noticed that sometimes on Data line I see a ~0.4V "tail". It stays at ~0.4V for over 1 clock period. It happens always with DIR going going low.

Is this something expected? Should I worry about this? Zynq VIL_MAX is 0.63V, so I have some margin, but VIL_MAX on TUSB1210 is 0.45V.

Thank you,

Rafal