Tool/software:

Hello,

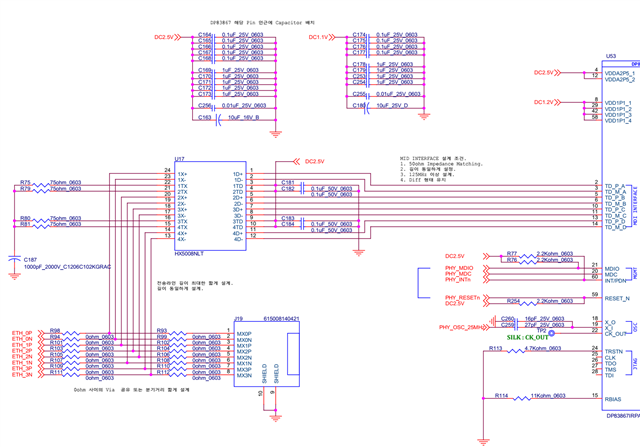

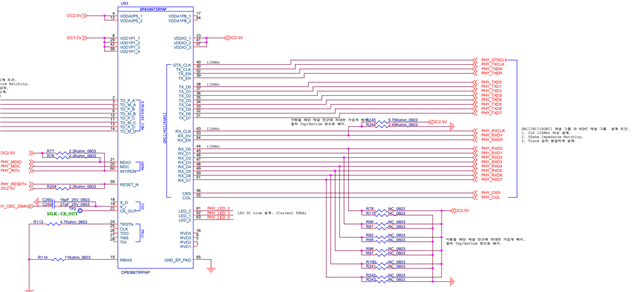

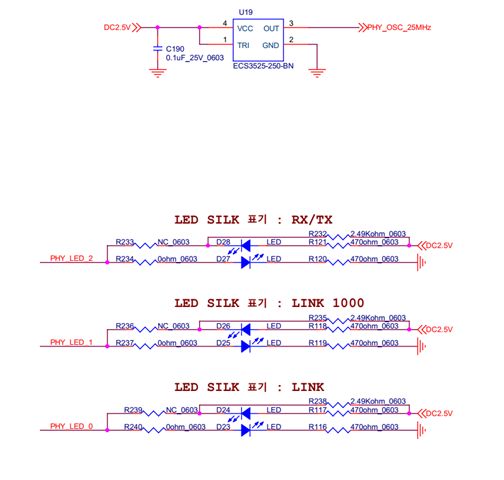

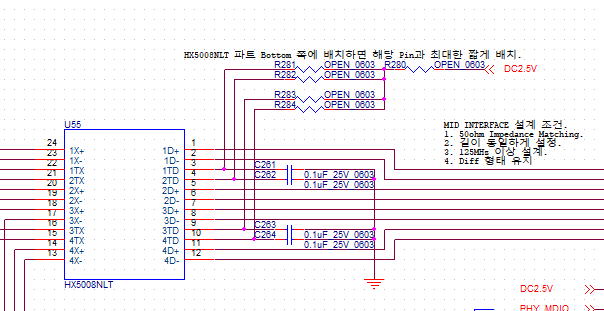

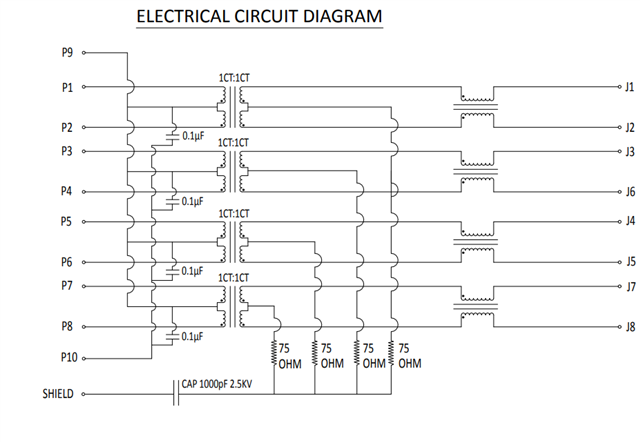

We have completed the circuit design for the DP83867IRPAP as outlined below.

This design is a revision of our existing product, replacing the Marvell 88E1111-BAB with the DP83867IRPAP.

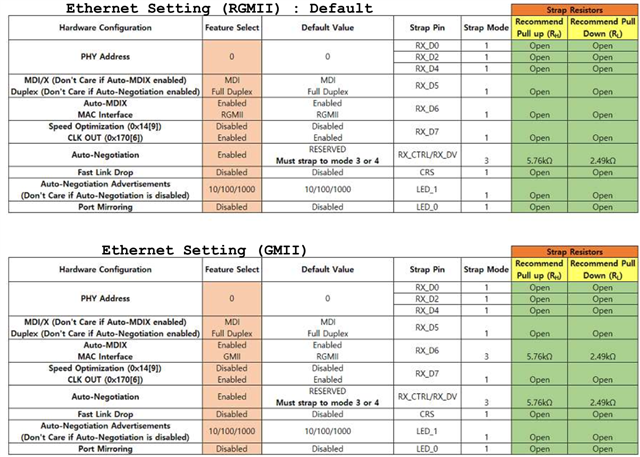

The default STRAP PIN configuration is RGMII. To verify compatibility with the existing FPGA firmware without any modifications, all STRAP PIN resistors have been applied so that the configuration can also be switched to GMII.

We would like to confirm if there are any potential issues or considerations with this configuration.

Thank you for your support.

Best regards,

Jun-Seok, Bae