Tool/software:

Hi,

Let me ask you a basic question about the "Via" design of the PCB design as below.

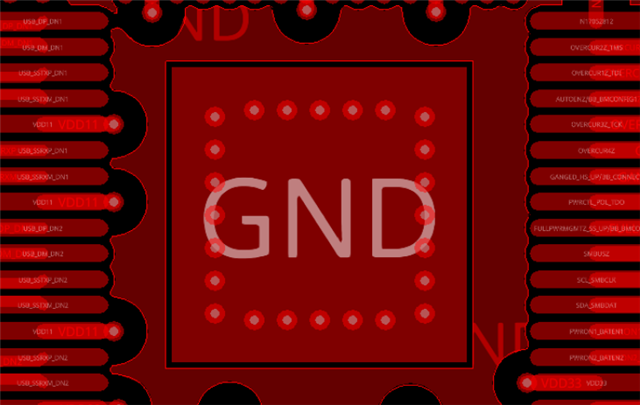

Regarding the "Vias" in the GND and thermal PAD located beneath of this device,

are ther any design requirements that are considered "mandatory" or "recommended" ?

Especially, "PAD on Via" and "Filled Via" are "mandatory" or "recommended" ?

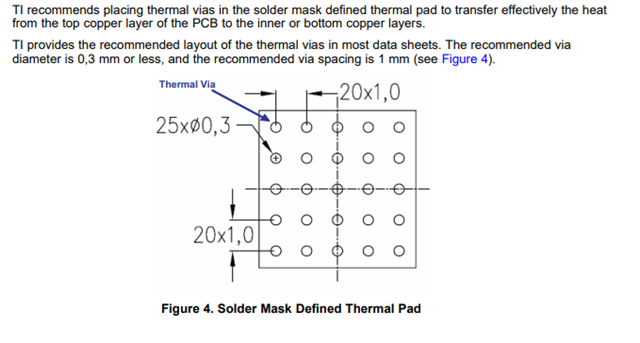

And your recommend PCB layout is the one which is on the datasheet, right?

The "Vias" which are shown on the datasheet are ”Unfilled Via”, correct?

Thank you for your support.

Best Regards,

Takumi