Other Parts Discussed in Thread: DS160PT801

Tool/software:

Hi Tech team ,

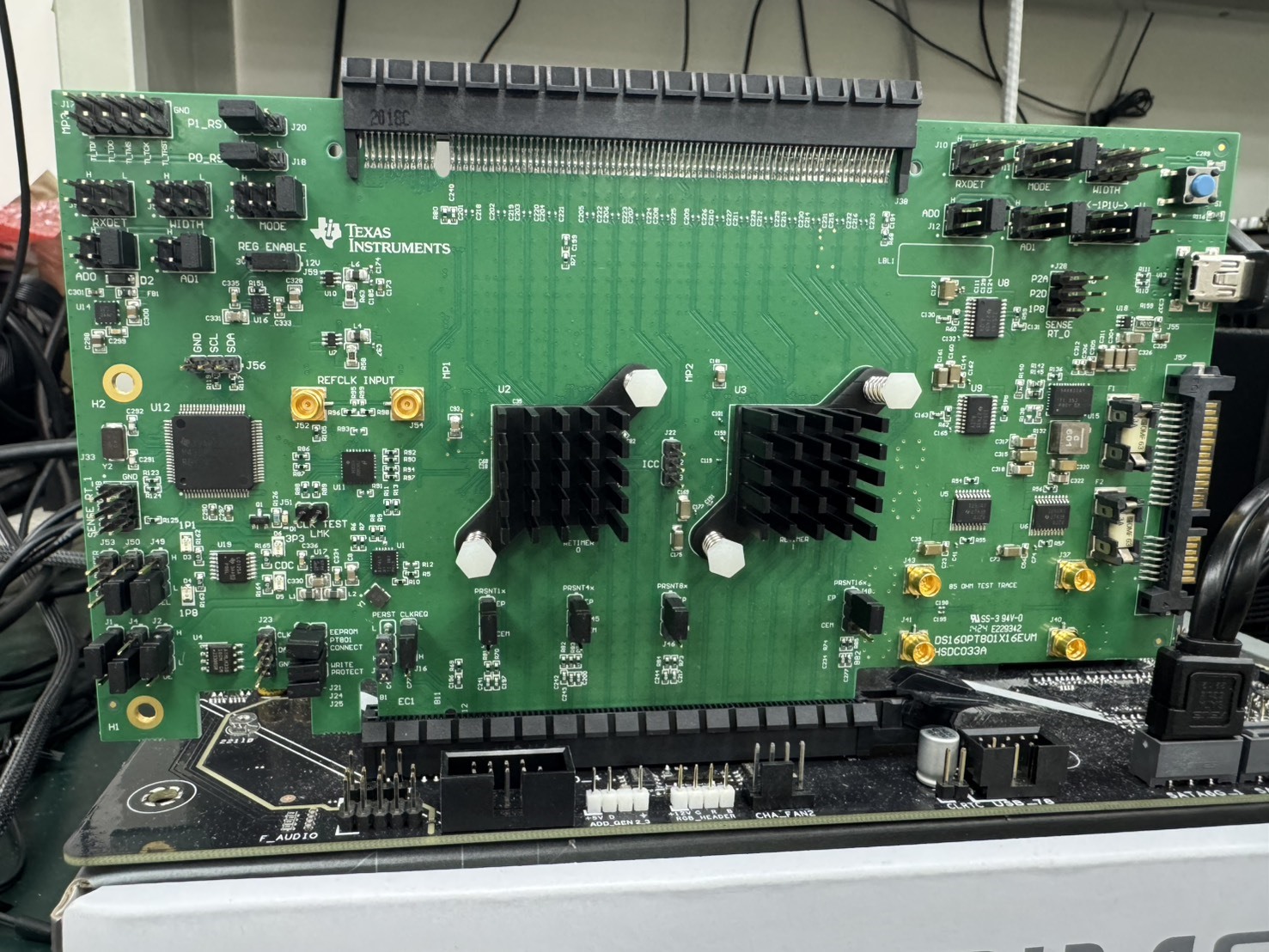

Here is Sparkle.Co

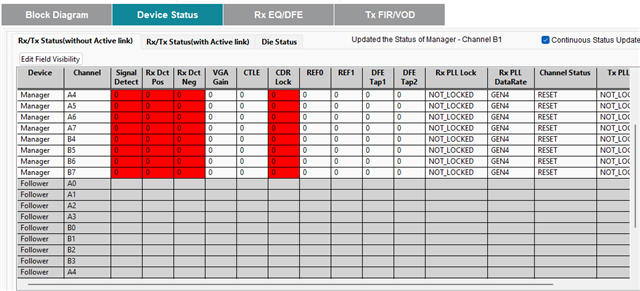

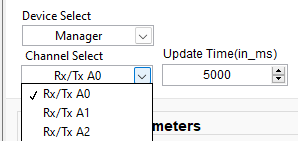

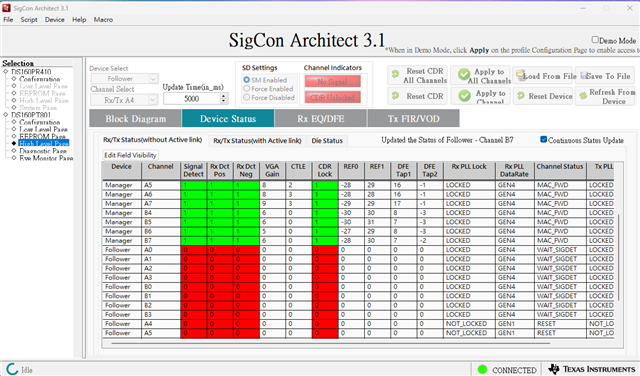

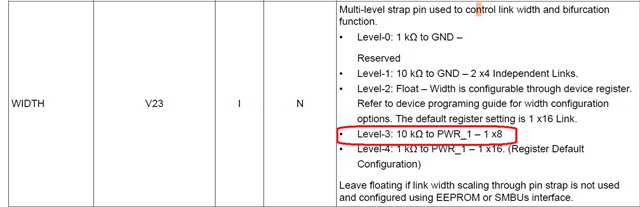

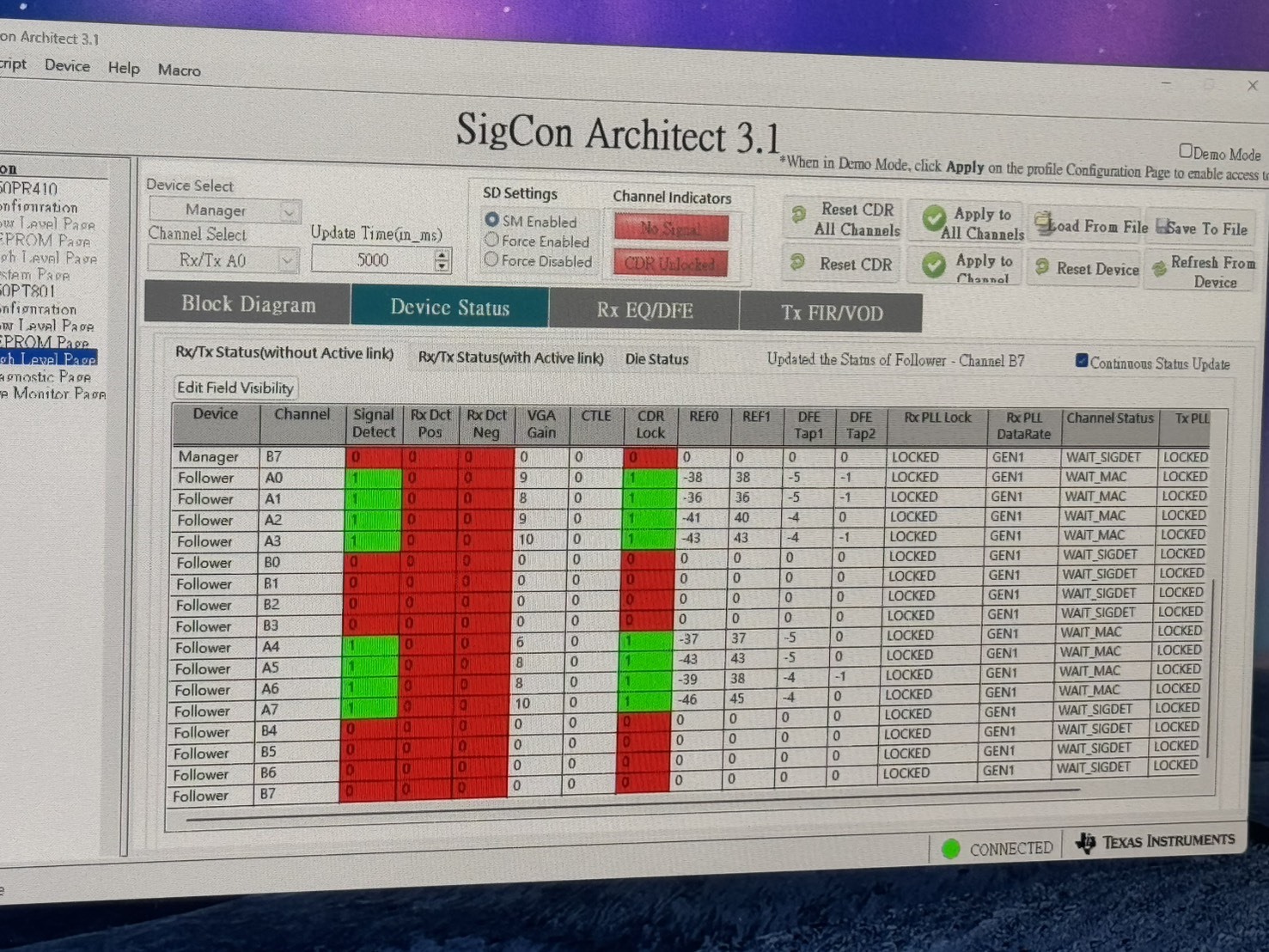

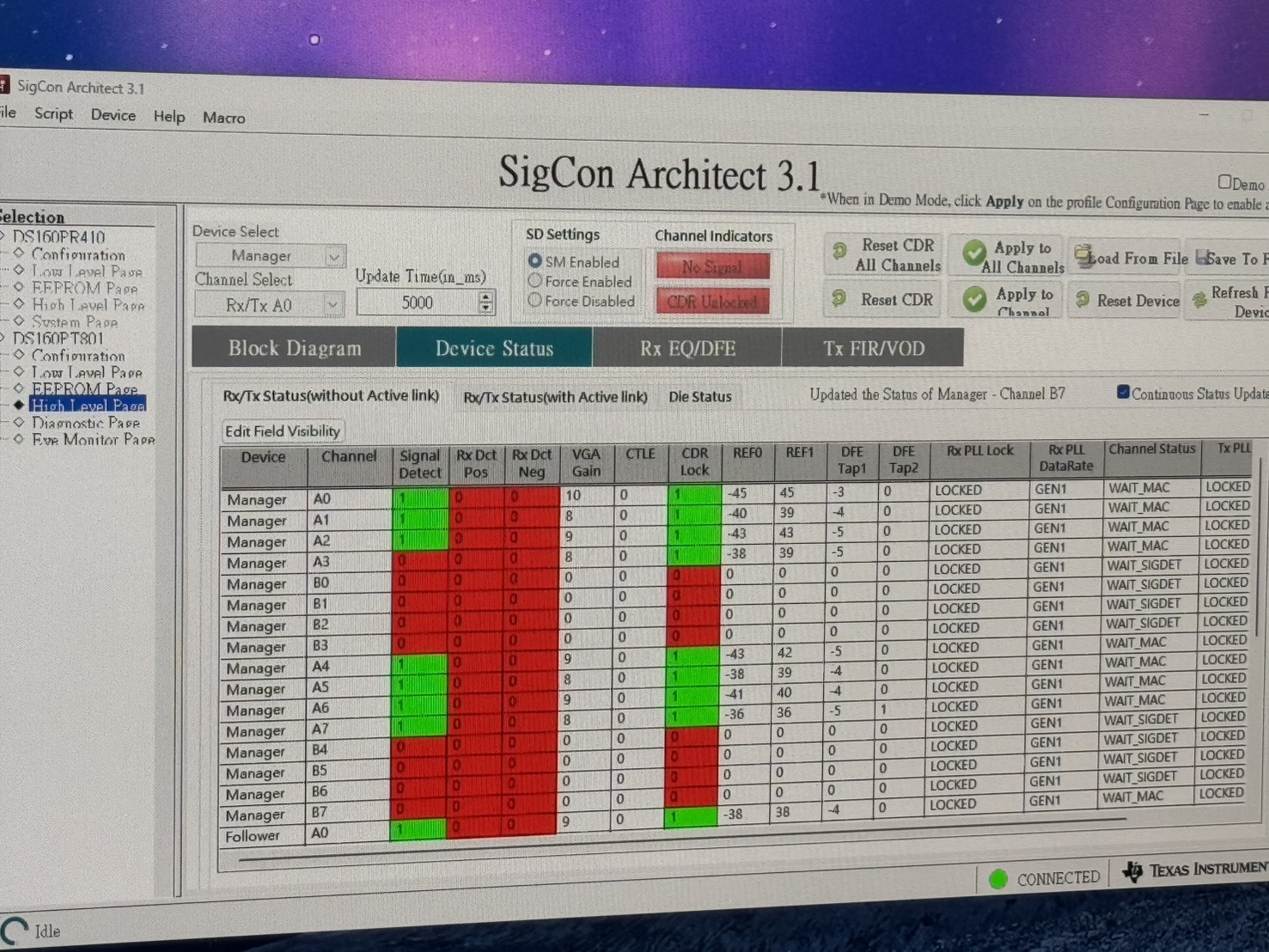

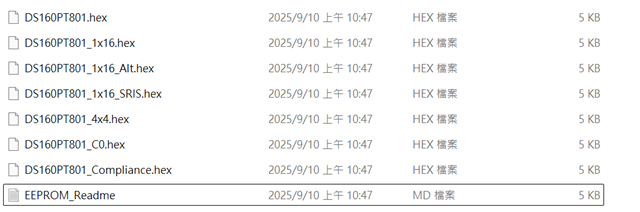

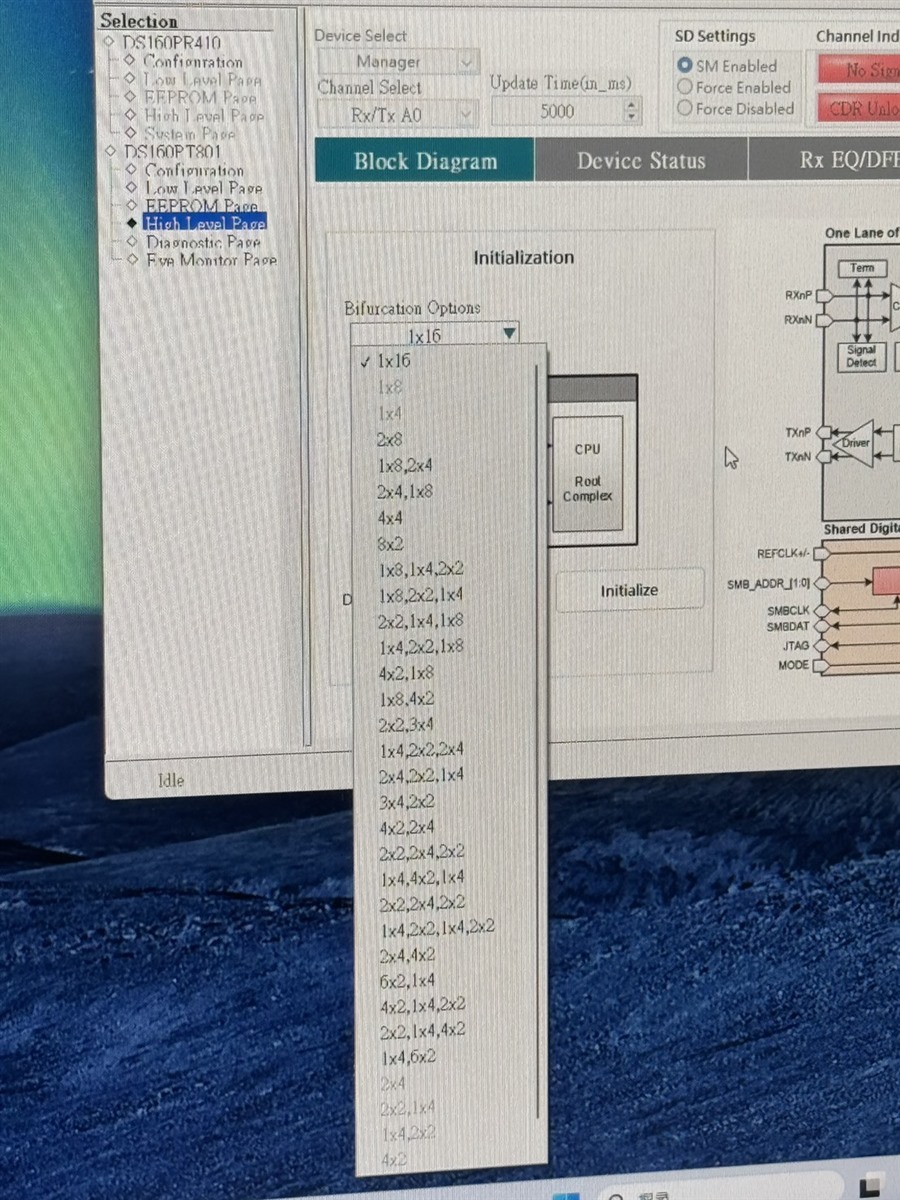

We have installed the GUI successfully and are able to connect to the EVM board. However, we are not sure how to fine-tune the configuration or how to measure the eye pattern. Is there any possibility that you could provide a live stream to teach us how to tune these parameters in the GUI and explain the definitions of those parameters? Since we do not have any technical support available here in Taiwan, we would greatly appreciate it if you could support us with a live stream or remote session.