Part Number: DP83867IR

Other Parts Discussed in Thread: AM62L

Tool/software:

Hello.

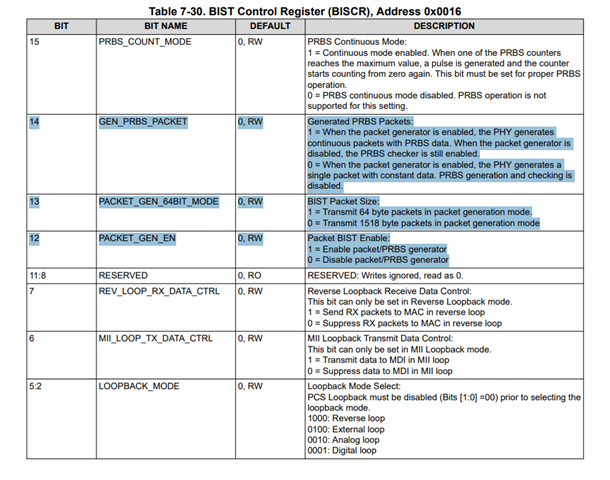

We currently have some issues with your Ethernet PHY DP83867IR and trying to troubleshoot it. And as it is hardly possible to measure the signals under the SoC for the RX lines, I would like to try to use the internal self test. I also found your APN for that, which roughly explains what to need to be done.

And here is my question: Is there an APN which actually explains how this is done in form of an example? Like what commands do I need to send, to the PHY? How do I check that the receiving packets are the same? Or can I just do an iperf command on myself?

Maybe you have something more practical which you are willing to share.

Cheers