Tool/software:

Hi,

1)What is the difference in nRST function when using the TLIN1431-Q1 in SPI mode vs Pin control mode? In the datasheet, it is specified as defaulted function in SPI mode.

![]()

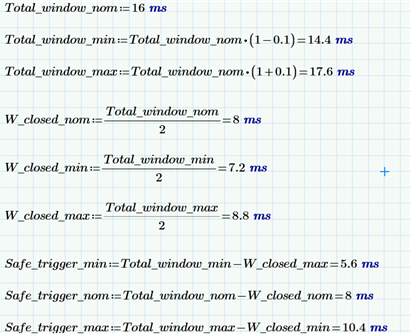

2)Whether the below listed values in the below table for SPI is total window time? For example, if we choose WD_TIMER as 000 and WD_PRE as 11, then chosen total window

time is 16ms?

3)Then whether watchdog has to be serviced with 5.6ms to 10.4ms for 16ms window selection?

Calculation:

4)What is the time duration between watchdog error and reset trigger time for SPI control mode? (I assume it depends on counter but considering it as a permanent fault - any number is available)

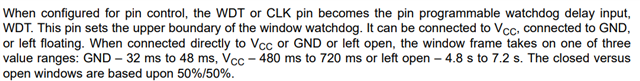

5)In pin control mode, it is mentioned that WDT sets upper boundary of the window watchdog. Whether the values listed , eg for GND - 32ms to 48ms is total window size?

6)What is meant by Current mode?

Thanks,

Sri Viswa