Part Number: SN65DSI86

Tool/software:

This going to deep for and I need your help. The board schematics needs to be ready next week Tuesday. appreciate your help.

Customer info:

Regarding the SN65DSI86:

In our last state of our carrier board we have designed the board to connect several video bridges to it. We have created a mini PCB with the DSI Bridge SN65DSI86 that is connected to our carrier board. The bridge of the mini PCB currently does not work. The Test picture is shown on the LCD (eDP lines of the bridge works fine) but the DSI communication between the SOM and the bridge has the error flag CHA_DSI_PROTOCOL_ERR is set. The DSI lines of the bridge are directly connected to the AVNET SOM with the IMX.85. If we connect the eval board of the SN65DSI86 to the DSI connector it works fine.

This is the reason why I ask you: can you please review our next design where the TI DSI bridge SN65DSI86 is integrated to the carrier board?

You can find the schematic page attached.

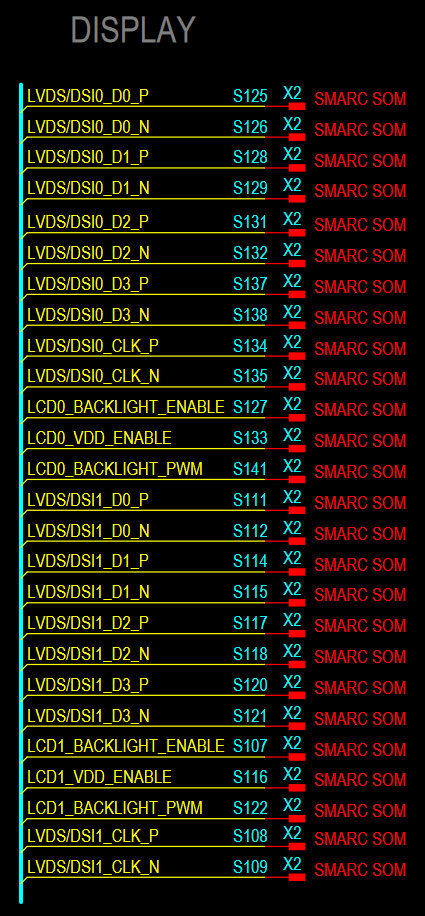

The connection to the SOM via the SMARC interface has the following pinout:

Do you have any other important points regarding the schematic of the bridge?

Would be nice to get a feedback until Tuesday next week from your side, because the schematic has to be finished next week.

----------

It is possible to set-up a call Dallas morning time as the customer is located in Germany. 1st prio is Schematic review. 2nd prio why the min PCB (daughtercard) doesn't work.