Part Number: SN75DP159

Other Parts Discussed in Thread: TMDS181, TUSB3410

Tool/software:

Hi Tier

Can DP159 support the Eye Scan function? If supported, could you give my customer some guide?

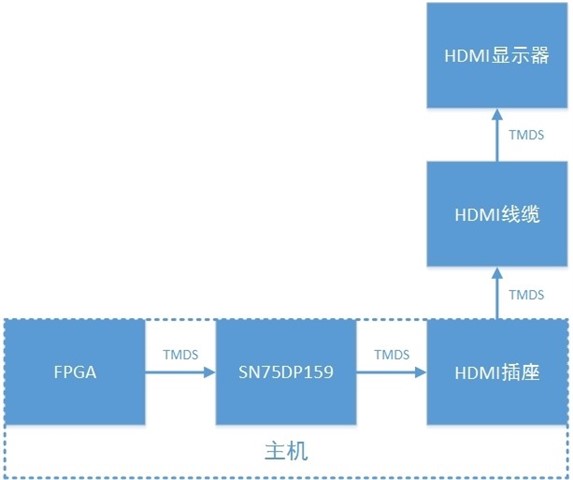

Can DP159's TMDS disparity or data errors be used to count the number of bit errors when TMDS is transmitted properly? In datashett , Do We only need set bit[7:4] of the 16h register to 1 to enable bit error statistics? but we tested it , it doesn't work .

Test method: Modify the data polarity of the FPGA's HDMI PHY output, DP159 doesn't have an increase in BERT_CNT. but the display SCDC register error is increased, Explain that modifying the data polarity can create a bit error scenario, not detected by DP159.

Do you know why , could you give some guidance.

Thank you very much.