Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Tool/software:

Hi all,

SOC: Zynq MPSoC (Xilinx/AMD)

MAC interface: GEM1

Phy & mode: DP83869 (TI) & RGMII copper

The interrupt is configured as Level triggered as below

&gem1 {

phy-mode = "rgmii-id";

status = "okay";

phy-handle = <&phy1>;

phy1: phy@1 {

reg = <1>;

compatible = "ethernet-phy-ieee802.3-c22";

rx-internal-delay-ps = <2000>;

tx-internal-delay-ps = <2000>;

interrupt-parent = <&gpio>;

interrupts = <78 8>; //EMIO 0 is used as INT

};

};

It is confirmed interrupt is configured using "macb ff0c0000.ethernet eth0: PHY [ff0c0000.ethernet-ffffffff:01] driver [TI DP83869] (irq=52)" and in cat /proc/interrupts also entry is there.

By default when no cable is connected, the INT line probes high & reads high. When cable is connected link is up, counter in cat /proc/interrupt is increased and the INT line probes low. But after link up, the interrupt line remains in low state which causes the spurious interrupt state and make the interrupt is disabled with below crash.

root@zynqmp-iwg36o:~# [ 1040.510999] irq 52: nobody cared (try booting with the "irqpoll" option)

[ 1040.517716] CPU: 0 PID: 0 Comm: swapper/0 Not tainted 6.6.40-xilinx-gf2d46953498a #1

[ 1040.525463] Hardware name: xlnx,zynqmp (DT)

[ 1040.529639] Call trace:

[ 1040.532077] dump_backtrace+0x90/0xe8

[ 1040.535749] show_stack+0x18/0x24

[ 1040.539073] dump_stack_lvl+0x48/0x60

[ 1040.542736] dump_stack+0x18/0x24

[ 1040.546051] __report_bad_irq+0x38/0x120

[ 1040.549975] note_interrupt+0x310/0x360

[ 1040.553811] handle_irq_event+0xd8/0xe8

[ 1040.557648] handle_fasteoi_irq+0xb0/0x284

[ 1040.561745] generic_handle_domain_irq+0x2c/0x44

[ 1040.566371] zynq_gpio_irqhandler+0xa0/0x16c

[ 1040.570642] generic_handle_domain_irq+0x2c/0x44

[ 1040.575268] gic_handle_irq+0x6c/0x9c

[ 1040.578931] call_on_irq_stack+0x24/0x4c

[ 1040.582855] do_interrupt_handler+0x80/0x84

[ 1040.587038] el1_interrupt+0x34/0x54

[ 1040.590614] el1h_64_irq_handler+0x18/0x24

[ 1040.594711] el1h_64_irq+0x64/0x68

[ 1040.598114] default_idle_call+0x28/0x3c

[ 1040.602037] do_idle+0xac/0x100

[ 1040.605180] cpu_startup_entry+0x34/0x3c

[ 1040.609103] kernel_init+0x0/0x1e0

[ 1040.612505] arch_post_acpi_subsys_init+0x0/0x8

[ 1040.617036] start_kernel+0x504/0x60c

[ 1040.620699] __primary_switched+0xbc/0xc4

[ 1040.624710] handlers:

[ 1040.626975] [<000000008cd40a2e>] irq_default_primary_handler threaded [<00000000054f5ea5>] phy_interrupt

[ 1040.636480] Disabling IRQ #52

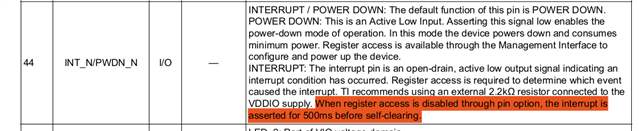

How to confirm if the PHY interrupt handler is invoked and serviced the interrupt (By reading the ISR register right)?

When reading the ISR register manually or in interrupt handler function after sometime it reads 0x0.

Please help in debugging why the interrupt remains low and not de-asserted.