Other Parts Discussed in Thread: AM6442, DP83869, TMDS64EVM

Tool/software:

Hi,

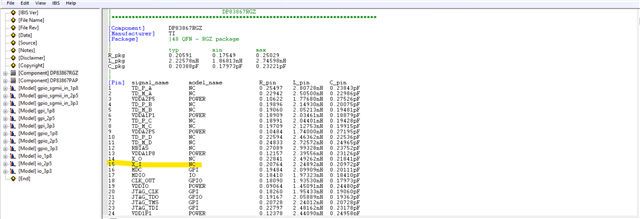

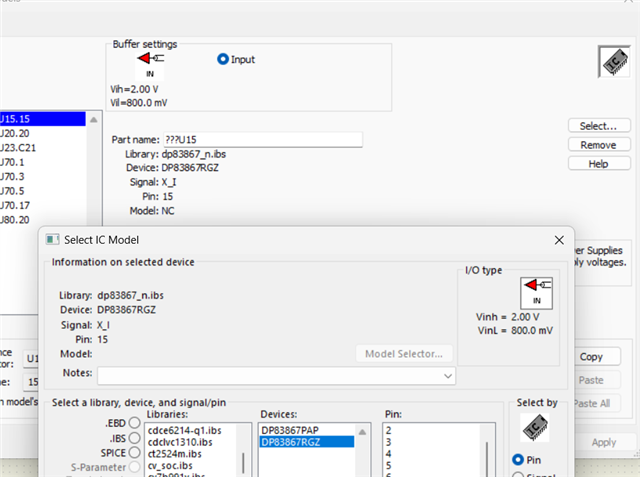

In the IBIS model for DP83867IRRGZT, pin 15 (X_I) is marked as NC, but the simulation wizard shows Vih as 2 V and Vil as 800 mV, which doesn’t match the 1.8 V logic level I’m using. The same issue is seen in the AM6442 processor, where pin C21 is also marked NC in the IBIS model. I’ve used the latest IBIS models from your website, and changing Vih/Vil values seems to affect undershoot/overshoot in simulations. Could you please clarify this? I will provide the snapshot for your reference.