Tool/software:

Hi Team,

The customer has some problems using FPD-LINK III. Please help me take a look. Thank you.

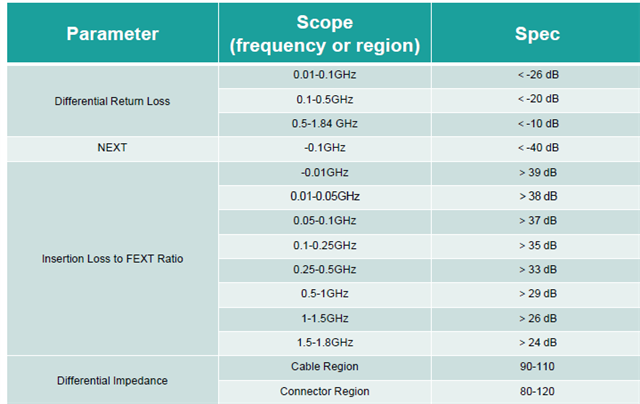

1. A customer's cockpit project currently uses the DS90UB949/947 (dual-channel HSD interface) deserializer chip. I'd like to understand the performance requirements (such as insertion loss and return loss) for the SI evaluation of cable harness selection. Are there any relevant design manuals or instructions available?

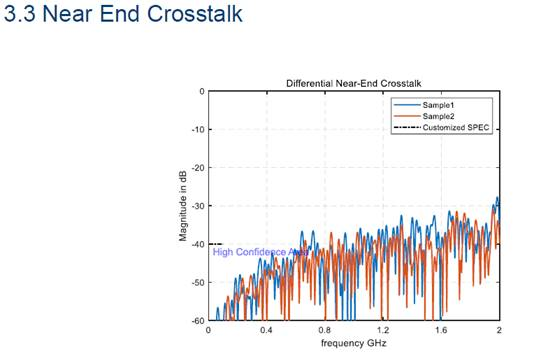

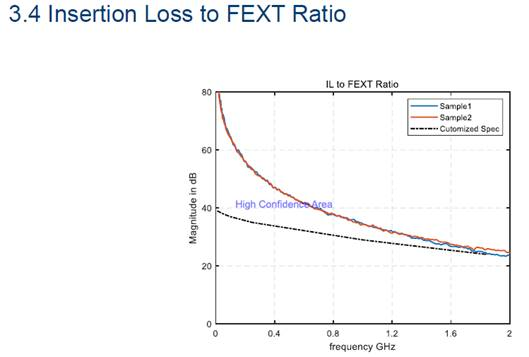

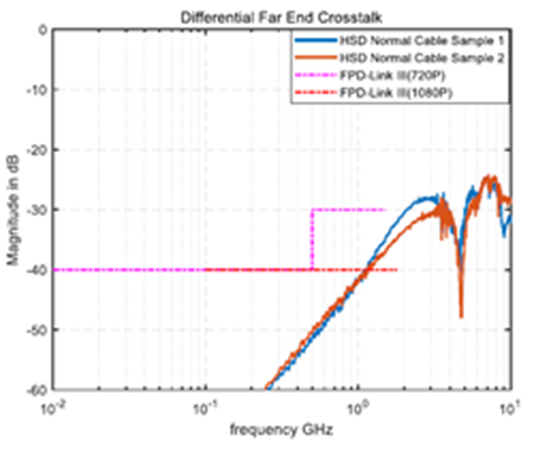

2.The customer plans to use a 4.5m HSD cable harness for their product. The following data is available for testing of a 4m cable harness. If the length is extended, the far-end crosstalk and near-end crosstalk performance may meet the standards. Is there any margin for these performance indicators on the chip side?

- 1) Are there any unreasonable requirements for the internally developed cable harness performance standards?

- 2) 4m test data, crosstalk data has reached the limit. If it is extended to 4.5m, is there any margin at the chip end? What is the standard of this data?

3. Does FPD-LINK III have an eye diagram test method document? How can customers test it? Can signal quality be judged using the eye diagram?