Other Parts Discussed in Thread: DP83869

Tool/software:

Hi I am having difficulty with the DP83869. I am able to communicate over MDIO but I am not able to establish comms.

The first suspicious thing we noticed is that there is no clk on ref_clk. Even though the mode reported is RGMII to copper

The below shows that we read the strap mode to be RGMII to copper and that the address is 0x3

root@taquito-tfc:/data$ ./mdio-ext read 0x6e

reading reg: 0x6e

0x0030

The next weird thing we noticed is that the PWD_DWN is high unless we override it over MDIO.

root@taquito-tfc:~$ mdio stmmac-1 3 0

0x1940

Here is a picture of our circuit

Strapping should be for RGMII to Copper (which we are reading properly over MDIO).

PWDN is pulled up as it is active low

Reset is also pulled up as it is active low

Once we override the pwd_dwn pin over mdio, we are still reading the CORE_PWR_MODE register to be all 0

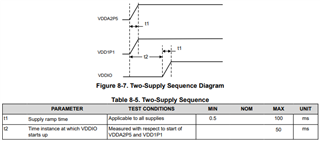

I am curious if anyone has experience using 2 power mode with VDDIO being 1.8V? As another thing we are noticing is that the VDDA1P8 pins are measuring to be 0V