Part Number: DP83822H

Tool/software:

Hello,

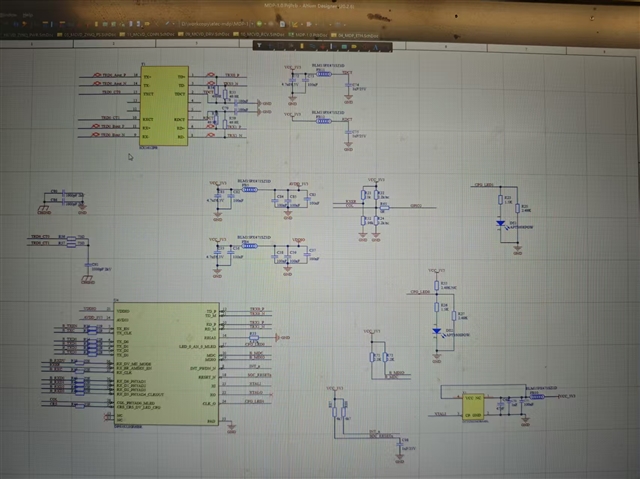

Problem 1: The customer uses FGPA (ZYNQ) to test DP83822HRHBR. If the RGMII interface is not connected to the FPGA, the PHY can be linked to the upper computer. If the RGMII is connected to the ETH0 pin of the FPGA, regardless of whether there is a driver on the FPGA, the PHY cannot be linked to the upper computer.

Problem 2: The RXD pin is not configured with pull-up and pull-down resistors. If connected to an FPGA, the address is not the default 01, but 1f, which means that the addresses of the RXD pin should all be 1. The customer tried to configure a 4.7K pull-down resistor for the RXD pin, but the address became 01, which should also be incorrect.

Please help analyze the reason, thank you!