Part Number: SN65DSI86

Other Parts Discussed in Thread: TS3DV621

Tool/software:

Hello,

We use the SN65DSI86 for a two-lane eDP connection. With our 15.6” FHD colour TFT-LCD display, the training link fails and we get a blank screen after 3 to 5 power cycles. The display is two-lane compatible and has a data rate of 2.7 Gbps per lane. If we reboot it, in most of the cases the next training link is successful but the problem is still very annoying.

Looking at error registers 0xf0–0xf8 of the SN65DSI86 DSI-to-DP bridge, during a failed cycle the register value is 0x12 (LT_EQ_LPCNT_ERR) instead of the expected 0x01 (Semi-Auto link training successful). This indicates that the link training failed in the channel equalization phase.

Looking at the link training register, if it fails, register `0x93` shows a value of `0xa4`, which means that pre-emphasis level 2 is set.

Register 0x94 shows a value of 0x81, which means voltage swing level 1. In a successful cycle, pre-emphasis and voltage swing are both always level 0.

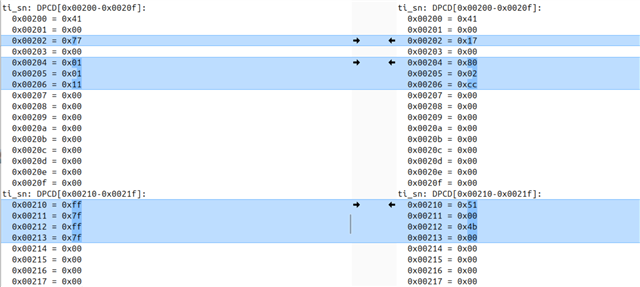

I also read the DPCD of the sink and compared the passing and failing cycles.

According to the DP standard, registers 0x103 and 0x104 set the output voltage and pre-emphasis levels respectively. In a failing cycle, these registers are set to the value `0x30`, which indicates a pre-emphasis level of 2 and that the maximum setting has been reached. This is the same as I could read out before from the bridge.

Left Pass, Righ Fail

Looking further, if it's a pass, I see register 0x202 has a value of 0x77, so CR and channel EQ have been completed and the symbol is locked for lanes 0 and 1.

However, if it fails, the value is `0x17`, meaning that the CR and channel EQ are complete and symbol is locked for lane 0 but lane 1 has the CR complete, but the channel EQ fails.

Registering a value of 0x00 instead of 0x01 in register 0x204 also shows me that interlane alignment was not successful.

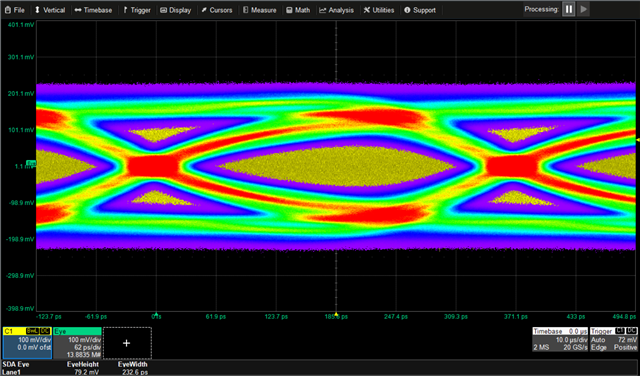

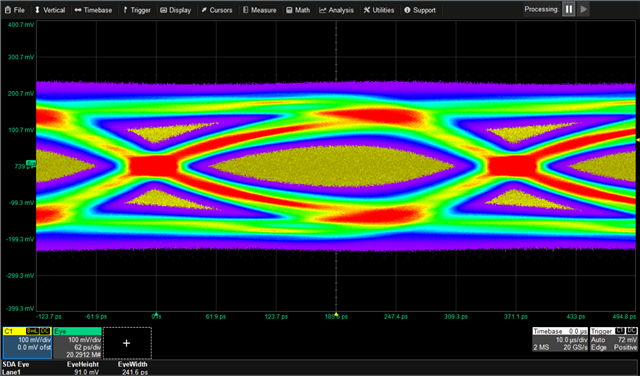

This all would point to a signal integrity issue in the main link, probably on lane 1, but looking at lane 0 and 1 the eye seems to be good enough. The measurement was done directly on the eDP connector.

channel 0:

channel 1:

Any ideas?

kind regards

Franz