Tool/software:

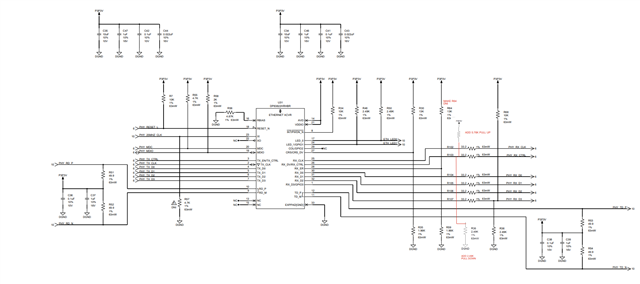

Hi, I am trying to interface PHY Dp83822H with FPGA. I am able to write and read PHY registers. It is configured for RMII, 100mbps, full duplex mode.

I am sending TX[1:0] and TEN signals to PHY from FPGA (Not using MAC). It is a generic Ethernet frame with UDP payload. Everything seems correct but I am not able to see anything on the wireshark. No transmit data is coming out of PHY.dp83822h_settings.xlsx