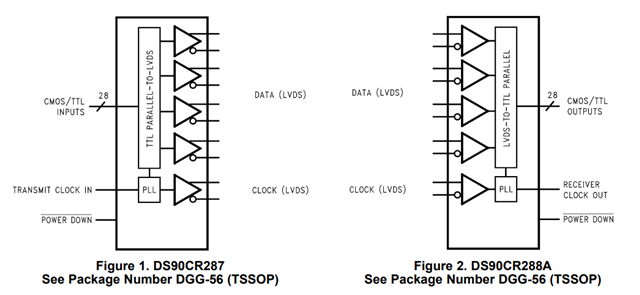

Part Number: DS90CR287

Other Parts Discussed in Thread: DS90CR288A,

Tool/software:

Hi everyone,

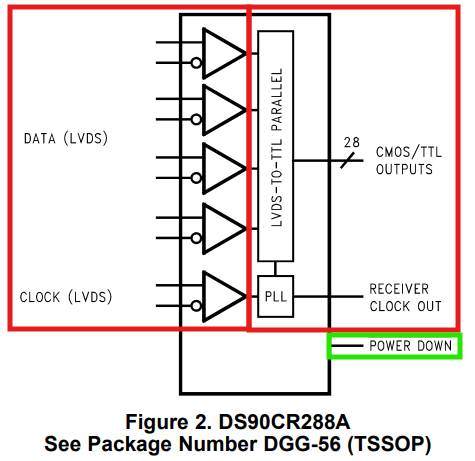

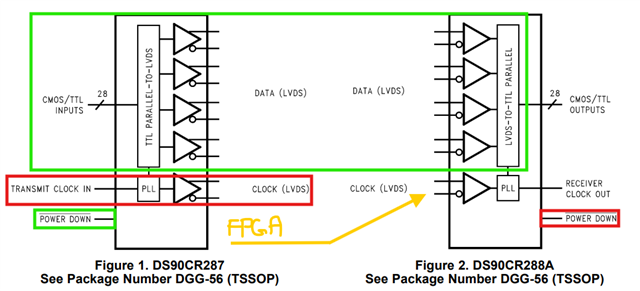

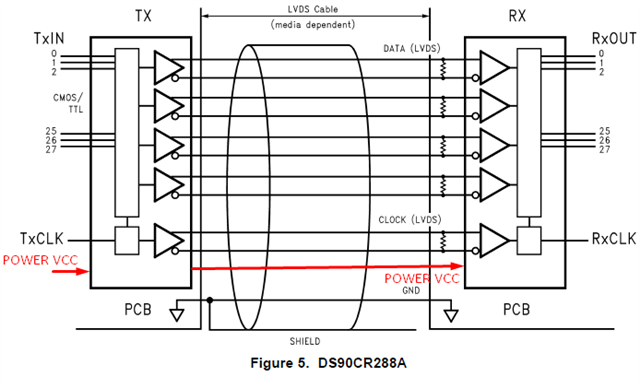

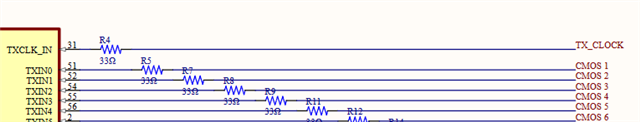

I have DS90CR287 for TX and DS90CR288A for RX chips. I tested before these chips (first power up) and i get clock and data with little noise. Design has decoupling capacitor. Then second power up i can not get any clock from TX side. I give diff clock with FPGA to RX chip, it is worked. Problem is TX side. My boot up sequence is below:

- TX power up ( PWRDWN is low)

- FPGA power up and give clock same time.

- TX PWRDWN is high.

So reference guide and other thread what i read , telling me this seqeuence. But i can not get any clock second power up section. Is it about chip or PLL? All voltages is 3.3 and ground is connected. (PLL,LVDS and VCC ext.) I changed IC 3 times and same results i get.

Thanks for reply.

Best regards,