Part Number: XIO2001

Tool/software:

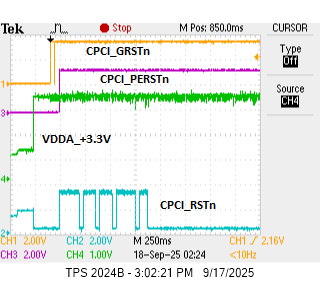

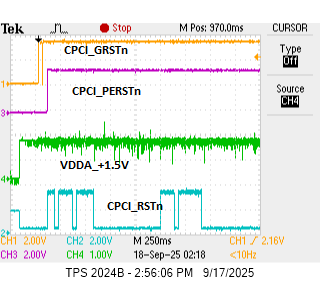

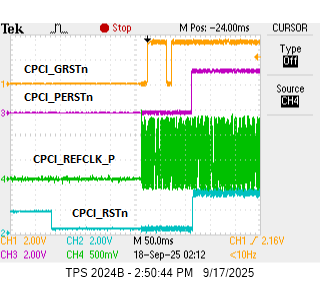

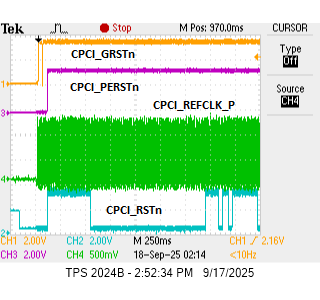

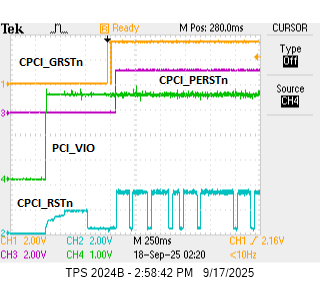

I have a new design that I am getting intermittent results on enumeration of cards on the cPCI port. When I look at the signals I see the (cPCI reset) PRSTn signal on the cPCI side is switching high and low over a few times over a few second period. It does this anywhere from 2 or 3 to 10 times. I verified the power up sequence meets the data sheet. The datasheet does not specify when GRSTn should get released in relation to the power up sequence. I have experimented with it before, after, and at the same time as (PCIe reset) PERSTn, but it does not make a difference. The activating and de-activating of PRSTn does not seem to correlate to anything else in the system.

When should GRSTn be released in relation to the rest of the power up diagram?

What other connections to the chip can I look at that would cause the PRSTn to toggle? The power rails, PERSTn, GRSTn, and the PCIe clock all look good.

Frank