Tool/software:

Dear Support Team,

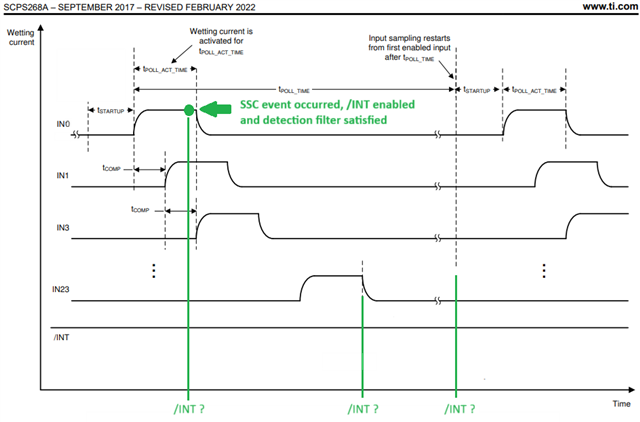

can you please detail when the /INT-pin is raised in polling mode after confirmed SSC:

* immediately when the SSC is detected?

* when all enabled input channels are "scanned" (at the end of the application of the wetting current of e.g. IN23)?

* at the end of the polling cycle?

Please identify in the attached diagram, when the signal at the /INT-pin is raised.

What is the delay from SSC detection to /INT raised?

Best regards,

Andreas