Other Parts Discussed in Thread: TCAN4550

Tool/software:

Hello Application Team:

we have design TCAN4550-Q1 , in the first time, we are trying to adding enable TX buffer interrupt after Tx send message complete.

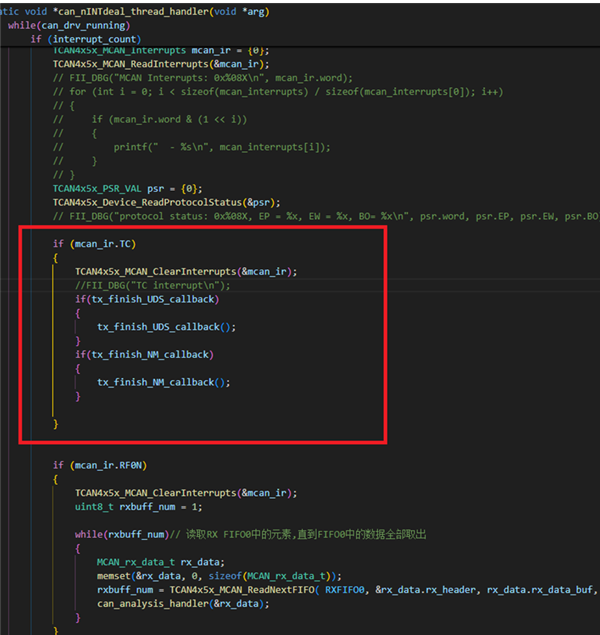

But we found RF0N: Rx FIFO 0 new message -> host cannot get any interrupt from TCAN4550-Q1 when Host send continuously CAN message after we adding enable TX buffer interrupt code.

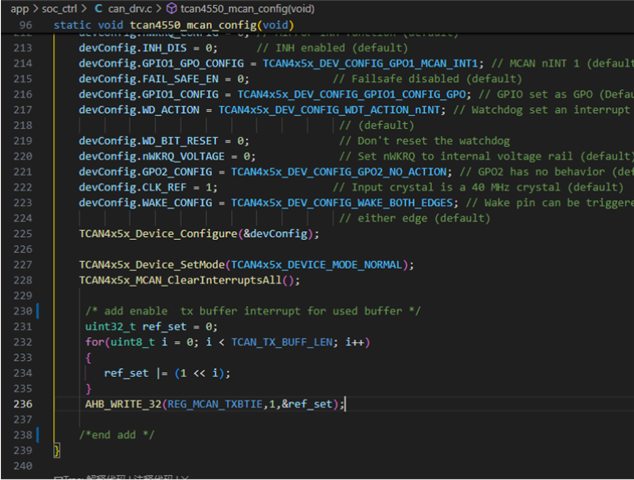

The following coding is we are adding to enable the TX buffer interrupt get TC interrupt when CAN message is compete. could you please help give suggestion of register set flow of TCAN4550 ?

Our Requirement:

(1)Need to get TCAN4550 TC interrupt to Host when Tx buffer complete:

(2)still need get RF0N: Rx FIFO 0 new message interrupt while CAN message is keep to working after implement Item 1 requirement.

Add TX buffer interrupt code get TC interrupt status when CAN message is compete as below