Other Parts Discussed in Thread: DS25BR204,

Tool/software:

Hi TI team.

Could you please provide information on the IO state of the output pins when /PWDN=L?

Regards,

Matsumoto

Tool/software:

Hi TI team.

Could you please provide information on the IO state of the output pins when /PWDN=L?

Regards,

Matsumoto

Hi Matsumoto-san,

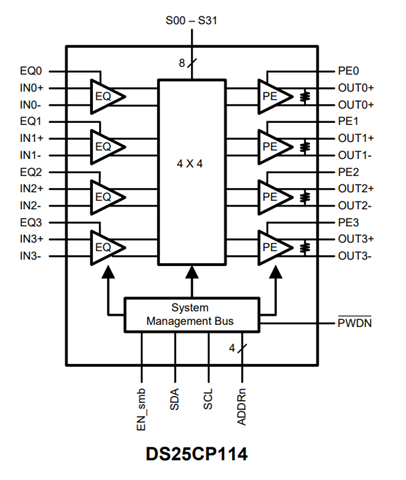

When PWDN=L, output pins will have differential voltage of 0V. Based on block diagram below, we expect output termination to remain present in power down.

Thanks,

Drew

Thank you for your response.

I would like to confirm my understanding: When the differential voltage is 0V,

does this mean that the common mode voltage is being output?

Could you please verify if this interpretation is correct?

Regards,

Matsumoto

Hi Matsumoto-san,

When differential voltage is 0V, this means OUT0+ - OUT0- = 0V.

From the data sheet, it's not completely clear to me how common mode voltage is being handled in power down condition. Unfortunately, I don't have a board available to check this on.

Thanks,

Drew

Thank you for your response.

I am inquiring precisely because this information is not included in the datasheet.

Would it be possible for you to verify this information internally on your end?

Regards,

Matsumoto

Hi Matsumoto-san,

Unfortunately due to the age of this device and lack of evaluation board, it's challenging to verify this.

I was able to locate a board for DS25BR204, which is a very similar device. When PWDN is set on this device, outputs maintain a common mode voltage of ~1.4V. We expect the same behavior from DS25CP104A.

Thanks,

Drew

Thank you for confirming the operation with DS25BR204.

I will use this information as a reference.

Regards,

Matsumoto