Tool/software:

Hi Sir/madam

Now, we have built a test framework , in this framwork, firstly Seneor output image data in DVP formal, by using DS90UB933EVM and DS90UB960EVM to realize finial MIPI ouput. However, from the oscilloscope collected MIPI output results, there is a situation of pixel loss.

we have used the 960EVM pattern generator mode to ruled out the possibility of loss in the section from 960 output to the oscilloscope. Now we suspect that there is a loss of pixels in the section from DVP output to DS90UB933EVM. I would like to ask if the 933EVM has the function to view the received DVP data, and another function compare the data input to DS90UB933EVM and the converted data into DS90UB960EVM.

i attach my register setting in below, if there is some need to modiy, also please tell me, thank you very much.

Register Data Name

0x0000 0x7A I2C_DEVICE_ID

0x0001 0x00 RESET_CTL

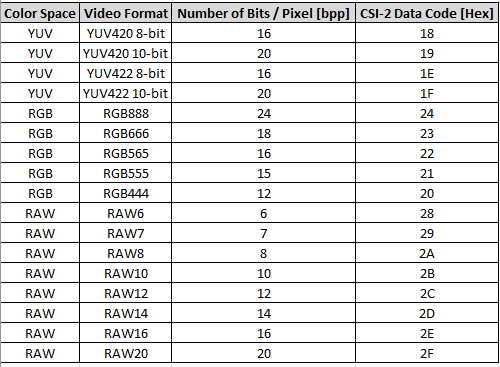

0x0002 0x1E GENERAL_CFG

0x0003 0x40 REV_MASK_ID

0x0004 0xD0 DEVICE_STS

0x0005 0x01 PAR_ERR_THOLD_HI

0x0006 0x00 PAR_ERR_THOLD_LO

0x0007 0xFE BCC_WATCHDOG_CONTROL

0x0008 0x1C I2C_CONTROL_1

0x0009 0x10 I2C_CONTROL_2

0x000A 0x7A SCL_HIGH_TIME

0x000B 0x7A SCL_LOW_TIME

0x000C 0x02 RX_PORT_CTL

0x000D 0xB9 IO_CTL

0x000E 0x00 GPIO_PIN_STS

0x000F 0xFF GPIO_INPUT_CTL

0x0010 0x00 GPIO0_PIN_CTL

0x0011 0x00 GPIO1_PIN_CTL

0x0012 0x00 GPIO2_PIN_CTL

0x0013 0x00 GPIO3_PIN_CTL

0x0014 0x00 GPIO4_PIN_CTL

0x0015 0x00 GPIO5_PIN_CTL

0x0016 0x00 GPIO6_PIN_CTL

0x0017 0x00 GPIO7_PIN_CTL

0x0018 0x00 FS_CTL

0x0019 0x00 FS_HIGH_TIME_1

0x001A 0x00 FS_HIGH_TIME_0

0x001B 0x00 FS_LOW_TIME_1

0x001C 0x00 FS_LOW_TIME_0

0x001D 0x00 MAX_FRM_HI

0x001E 0x04 MAX_FRM_LO

0x001F 0x05 CSI_PLL_CTL

0x0020 0xD2 FWD_CTL1

0x0021 0x03 FWD_CTL2

0x0022 0x08 FWD_STS

0x0023 0x00 INTERRUPT_CTL

0x0024 0x00 INTERRUPT_STS

0x0025 0x00 TS_CONFIG

0x0026 0x00 TS_CONTROL

0x0027 0x00 TS_LINE_HI

0x0028 0x00 TS_LINE_LO

0x0029 0x00 TS_STATUS

0x002A 0x00 TIMESTAMP_P0_HI

0x002B 0x00 TIMESTAMP_P0_LO

0x002C 0x00 TIMESTAMP_P1_HI

0x002D 0x00 TIMESTAMP_P1_LO

0x002E 0x00 TIMESTAMP_P2_HI

0x002F 0x00 TIMESTAMP_P2_LO

0x0030 0x00 TIMESTAMP_P3_HI

0x0031 0x00 TIMESTAMP_P3_LO

0x0032 0x00 CSI_PORT_SEL

0x0033 0x02 CSI_CTL

0x0034 0x00 CSI_CTL2

0x0035 0x00 CSI_STS

0x0036 0x00 CSI_TX_ICR

0x0037 0x00 CSI_TX_ISR

0x0041 0xA9 SFILTER_CFG

0x0042 0x71 AEQ_CTL

0x0043 0x01 AEQ_ERR_THOLD

0x0046 0x20 BCC_ERR_CTL

0x0047 0x00 BCC_STATUS

0x004A 0x10 FPD3_CAP

0x004B 0x12 RAW_EMBED_DTYPE

0x004C 0x00 FPD3_PORT_SEL

0x004D 0x00 RX_PORT_STS1

0x004E 0x02 RX_PORT_STS2

0x004F 0x00 RX_FREQ_HIGH

0x0050 0x00 RX_FREQ_LOW

0x0051 0x00 SENSOR_STS_0

0x0052 0x00 SENSOR_STS_1

0x0053 0x00 SENSOR_STS_2

0x0054 0x00 SENSOR_STS_3

0x0055 0x00 RX_PAR_ERR_HI

0x0056 0x00 RX_PAR_ERR_LO

0x0057 0x00 BIST_ERR_COUNT

0x0058 0x18 BCC_CONFIG

0x0059 0x00 DATAPATH_CTL1

0x005B 0x00 SER_ID

0x005C 0x00 SER_ALIAS_ID

0x005D 0x00 TARGET_ID_0

0x005E 0x00 TARGET_ID_1

0x005F 0x00 TARGET_ID_2

0x0060 0x00 TARGET_ID_3

0x0061 0x00 TARGET_ID_4

0x0062 0x00 TARGET_ID_5

0x0063 0x00 TARGET_ID_6

0x0064 0x00 TARGET_ID_7

0x0065 0x00 TARGET_ALIAS_0

0x0066 0x00 TARGET_ALIAS_1

0x0067 0x00 TARGET_ALIAS_2

0x0068 0x00 TARGET_ALIAS_3

0x0069 0x00 TARGET_ALIAS_4

0x006A 0x00 TARGET_ALIAS_5

0x006B 0x00 TARGET_ALIAS_6

0x006C 0x00 TARGET_ALIAS_7

0x006D 0x7D PORT_CONFIG

0x006E 0x88 BC_GPIO_CTL0

0x006F 0x88 BC_GPIO_CTL1

0x0070 0x2B RAW10_ID

0x0071 0x2C RAW12_ID

0x0072 0x00 CSI_VC_MAP

0x0073 0x00 LINE_COUNT_1

0x0074 0x00 LINE_COUNT_0

0x0075 0x00 LINE_LEN_1

0x0076 0x00 LINE_LEN_0

0x0077 0xC5 FREQ_DET_CTL

0x0078 0x00 MAILBOX_0

0x0079 0x01 MAILBOX_1

0x007A 0x00 CSI_RX_STS

0x007B 0x00 CSI_ERR_COUNTER

0x007C 0x20 PORT_CONFIG2

0x007D 0x00 PORT_PASS_CTL

0x007E 0x00 SEN_INT_RISE_CTL

0x007F 0x00 SEN_INT_FALL_CTL

0x0090 0x00 Reserved

0x0091 0x00 CSI0_FRAME_COUNT_LO

0x0092 0x00 CSI0_FRAME_ERR_COUNT_HI

0x0093 0x00 CSI0_FRAME_ERR_COUNT_LO

0x0094 0x00 CSI0_LINE_COUNT_HI

0x0095 0x00 CSI0_LINE_COUNT_LO

0x0096 0x00 CSI0_LINE_ERR_COUNT_HI

0x0097 0x00 CSI0_LINE_ERR_COUNT_LO

0x0098 0x1A CSI1_FRAME_COUNT_HI

0x0099 0x06 CSI1_FRAME_COUNT_LO

0x009A 0x01 CSI1_FRAME_ERR_COUNT_HI

0x009B 0x7F CSI1_FRAME_ERR_COUNT_LO

0x009C 0xFF CSI1_LINE_COUNT_HI

0x009D 0xFF CSI1_LINE_COUNT_LO

0x009E 0xFF CSI1_LINE_ERR_COUNT_HI

0x009F 0xFF CSI1_LINE_ERR_COUNT_LO

0x00A5 0x1C REFCLK_FREQ

0x00B0 0x02 IND_ACC_CTL

0x00B1 0x1F IND_ACC_ADDR

0x00B2 0x00 IND_ACC_DATA

0x00B3 0x08 BIST_CTL

0x00B6 0x18 PAR_ERR_CTRL

0x00B8 0xFD MODE_IDX_STS

0x00B9 0x33 LINK_ERROR_COUNT

0x00BA 0x83 FPD3_ENC_CTL

0x00BC 0x80 FV_MIN_TIME

0x00BE 0x00 GPIO_PD_CTL

0x00D0 0x00 PORT_DEBUG

0x00D2 0x94 AEQ_CTL2

0x00D3 0x09 AEQ_STATUS

0x00D4 0x23 ADAPTIVE_EQ_BYPASS

0x00D5 0xF2 AEQ_MIN_MAX

0x00D6 0x00 SFILTER_STS_0

0x00D7 0x00 SFILTER_STS_1

0x00D8 0x00 PORT_ICR_HI

0x00D9 0x00 PORT_ICR_LO

0x00DA 0x00 PORT_ISR_HI

0x00DB 0x00 PORT_ISR_LO

0x00DC 0x00 FC_GPIO_STS

0x00DD 0x00 FC_GPIO_ICR

0x00DE 0x00 SEN_INT_RISE_STS

0x00DF 0x00 SEN_INT_FALL_STS

0x00F0 0x5F FPD3_RX_ID0

0x00F1 0x55 FPD3_RX_ID1

0x00F2 0x42 FPD3_RX_ID2

0x00F3 0x39 FPD3_RX_ID3

0x00F4 0x36 FPD3_RX_ID4

0x00F5 0x30 FPD3_RX_ID5

0x00F8 0x00 I2C_RX0_ID

0x00F9 0x00 I2C_RX1_ID

0x00FA 0x00 I2C_RX2_ID

0x00FB 0x00 I2C_RX3_ID

Best Regards,

Gong bin